Public Member Functions | |

| DRC_TEST_PROVIDER_MATCHED_LENGTH () | |

| virtual | ~DRC_TEST_PROVIDER_MATCHED_LENGTH ()=default |

| virtual bool | Run () override |

| Run this provider against the given PCB with configured options (if any). | |

| virtual const wxString | GetName () const override |

| void | SetDRCEngine (DRC_ENGINE *engine) |

| bool | RunTests (EDA_UNITS aUnits) |

| EDA_UNITS | GetUserUnits () const |

| void | SetUserUnits (EDA_UNITS aUnits) |

| virtual void | GetUnitPair (EDA_UNITS &aPrimaryUnit, EDA_UNITS &aSecondaryUnits) |

| const EDA_IU_SCALE & | GetIuScale () const |

| virtual ORIGIN_TRANSFORMS & | GetOriginTransforms () |

| wxString | StringFromValue (double aValue, bool aAddUnitLabel=false, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| Converts aValue in internal units into a united string. | |

| wxString | StringFromValue (const EDA_ANGLE &aValue, bool aAddUnitLabel=false) const |

| wxString | StringFromOptionalValue (std::optional< int > aValue, bool aAddUnitLabel=false, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| Converts an optional aValue in internal units into a united string. | |

| wxString | MessageTextFromValue (double aValue, bool aAddUnitLabel=true, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| A lower-precision version of StringFromValue(). | |

| wxString | MessageTextFromValue (const EDA_ANGLE &aValue, bool aAddUnitLabel=true) const |

| wxString | MessageTextFromUnscaledValue (double aValue, bool aAddUnitLabel=true, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| wxString | MessageTextFromMinOptMax (const MINOPTMAX< int > &aValue, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| int | ValueFromString (const wxString &aTextValue, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| Converts aTextValue in aUnits to internal units used by the frame. | |

| std::optional< int > | OptionalValueFromString (const wxString &aTextValue, EDA_DATA_TYPE aType=EDA_DATA_TYPE::DISTANCE) const |

| Converts aTextValue in aUnits to internal units used by the frame. | |

| EDA_ANGLE | AngleValueFromString (const wxString &aTextValue) const |

| EDA_UNITS | GetUnitsFromType (EDA_DATA_TYPE aType) const |

| Gets the units to use in the conversion based on the underlying user units. | |

Static Public Member Functions | |

| static void | Init () |

| static EDA_DATA_TYPE | GetTypeFromUnits (const EDA_UNITS aUnits) |

| Gets the inferred type from the given units. | |

Static Public Attributes | |

| static const wxString | NullUiString = "" |

| The string that is used in the UI to represent a null value. | |

Protected Member Functions | |

| int | forEachGeometryItem (const std::vector< KICAD_T > &aTypes, const LSET &aLayers, const std::function< bool(BOARD_ITEM *)> &aFunc) |

| REPORTER * | getLogReporter () const |

| void | reportViolation (std::shared_ptr< DRC_ITEM > &item, const VECTOR2I &aMarkerPos, int aMarkerLayer, const std::function< void(PCB_MARKER *)> &aPathGenerator=[](PCB_MARKER *){}) |

| void | reportTwoPointGeometry (std::shared_ptr< DRC_ITEM > &aDrcItem, const VECTOR2I &aMarkerPos, const VECTOR2I &ptA, const VECTOR2I &ptB, PCB_LAYER_ID aLayer) |

| void | reportTwoShapeGeometry (std::shared_ptr< DRC_ITEM > &aDrcItem, const VECTOR2I &aMarkerPos, const SHAPE *aShape1, const SHAPE *aShape2, PCB_LAYER_ID aLayer, int aDistance) |

| void | reportTwoItemGeometry (std::shared_ptr< DRC_ITEM > &aDrcItem, const VECTOR2I &aMarkerPos, const BOARD_ITEM *aItem1, const BOARD_ITEM *aItem2, PCB_LAYER_ID aLayer, int aDistance) |

| virtual bool | reportProgress (size_t aCount, size_t aSize, size_t aDelta=1) |

| virtual bool | reportPhase (const wxString &aStageName) |

| bool | isInvisibleText (const BOARD_ITEM *aItem) const |

| wxString | formatMsg (const wxString &aFormatString, const wxString &aSource, double aConstraint, double aActual, EDA_DATA_TYPE aDataType=EDA_DATA_TYPE::DISTANCE) |

| wxString | formatMsg (const wxString &aFormatString, const wxString &aSource, const EDA_ANGLE &aConstraint, const EDA_ANGLE &aActual) |

Protected Attributes | |

| DRC_ENGINE * | m_drcEngine |

| bool | m_isRuleDriven = true |

Static Protected Attributes | |

| static std::vector< KICAD_T > | s_allBasicItems |

| static std::vector< KICAD_T > | s_allBasicItemsButZones |

Private Types | |

| using | CONNECTION = DRC_LENGTH_REPORT::ENTRY |

Private Member Functions | |

| bool | runInternal (bool aDelayReportMode=false) |

| void | checkLengths (const DRC_CONSTRAINT &aConstraint, const std::vector< CONNECTION > &aMatchedConnections) |

| void | checkSkews (const DRC_CONSTRAINT &aConstraint, const std::vector< CONNECTION > &aMatchedConnections) |

| void | checkViaCounts (const DRC_CONSTRAINT &aConstraint, const std::vector< CONNECTION > &aMatchedConnections) |

| void | checkStubLengths (const DRC_CONSTRAINT &aConstraint, DRC_RULE *aRule, const std::vector< CONNECTION > &aMatchedConnections) |

| void | checkReturnPath (const DRC_CONSTRAINT &aConstraint, DRC_RULE *aRule, const std::map< wxString, CONNECTION > &aChainAgg) |

| std::shared_ptr< CHAIN_TOPOLOGY > | chainTopologyFor (const wxString &aChain) |

| SHAPE_POLY_SET * | zoneUnionFor (PCB_LAYER_ID aRefLayer, const wxString &aRefNet) |

Private Attributes | |

| BOARD * | m_board |

| DRC_LENGTH_REPORT | m_report |

| std::map< wxString, std::shared_ptr< CHAIN_TOPOLOGY > > | m_chainTopoCache |

| std::map< std::pair< PCB_LAYER_ID, wxString >, SHAPE_POLY_SET > | m_refUnionCache |

| const EDA_IU_SCALE & | m_iuScale |

| EDA_UNITS | m_userUnits |

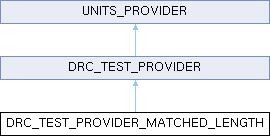

Detailed Description

Definition at line 50 of file drc_test_provider_matched_length.cpp.

Member Typedef Documentation

◆ CONNECTION

|

private |

Definition at line 67 of file drc_test_provider_matched_length.cpp.

Constructor & Destructor Documentation

◆ DRC_TEST_PROVIDER_MATCHED_LENGTH()

|

inline |

Definition at line 53 of file drc_test_provider_matched_length.cpp.

References m_board.

◆ ~DRC_TEST_PROVIDER_MATCHED_LENGTH()

|

virtualdefault |

Member Function Documentation

◆ AngleValueFromString()

|

inlineinherited |

Definition at line 195 of file units_provider.h.

References DEGREES, DEGREES_T, EDA_UNIT_UTILS::UI::DoubleValueFromString(), and GetIuScale().

◆ chainTopologyFor()

|

private |

Definition at line 647 of file drc_test_provider_matched_length.cpp.

References m_board, and m_chainTopoCache.

Referenced by checkStubLengths(), and runInternal().

◆ checkLengths()

|

private |

Definition at line 101 of file drc_test_provider_matched_length.cpp.

References _, DRC_ITEM::Create(), DISTANCE, DRCE_LENGTH_OUT_OF_RANGE, DRC_TEST_PROVIDER::formatMsg(), DRC_CONSTRAINT::GetName(), DRC_CONSTRAINT::GetOption(), DRC_CONSTRAINT::GetParentRule(), DRC_CONSTRAINT::GetValue(), MINOPTMAX< T >::HasMax(), MINOPTMAX< T >::HasMin(), MINOPTMAX< T >::Max(), MINOPTMAX< T >::Min(), DRC_TEST_PROVIDER::reportViolation(), TIME, and DRC_CONSTRAINT::TIME_DOMAIN.

Referenced by runInternal().

◆ checkReturnPath()

|

private |

Definition at line 840 of file drc_test_provider_matched_length.cpp.

References _, ARC_HIGH_DEF, SHAPE_POLY_SET::BBox(), SHAPE_POLY_SET::BooleanAdd(), SHAPE_POLY_SET::BooleanIntersection(), SHAPE_POLY_SET::BooleanSubtract(), BOX2< Vec >::Centre(), DRC_ITEM::Create(), DRCE_NET_CHAIN_RETURN_PATH_BREAK, ERROR_INSIDE, find, EDA_ITEM::GetBoundingBox(), BOARD_CONNECTED_ITEM::GetLayer(), BOX2< Vec >::Inflate(), SHAPE_POLY_SET::Inflate(), BOX2< Vec >::Intersects(), m_board, DRC_CONSTRAINT::m_ReferenceLayer, DRC_CONSTRAINT::m_ReferenceNet, SHAPE_POLY_SET::OutlineCount(), PCB_ARC_T, PCB_TRACE_T, DRC_TEST_PROVIDER::reportViolation(), ROUND_ALL_CORNERS, SHAPE_POLY_SET::Simplify(), BOARD_ITEM::TransformShapeToPolygon(), EDA_ITEM::Type(), UNDEFINED_LAYER, and zoneUnionFor().

Referenced by runInternal().

◆ checkSkews()

|

private |

Definition at line 176 of file drc_test_provider_matched_length.cpp.

References _, DRC_ITEM::Create(), DISTANCE, DRCE_SKEW_OUT_OF_RANGE, DRC_CONSTRAINT::GetName(), NETINFO_ITEM::GetNetCode(), DRC_CONSTRAINT::GetOption(), DRC_CONSTRAINT::GetParentRule(), DRC_CONSTRAINT::GetValue(), MINOPTMAX< T >::HasMax(), MINOPTMAX< T >::HasMin(), KiROUND(), m_board, MINOPTMAX< T >::Max(), UNITS_PROVIDER::MessageTextFromValue(), MINOPTMAX< T >::Min(), DRC_TEST_PROVIDER::reportViolation(), DRC_CONSTRAINT::SKEW_WITHIN_DIFF_PAIRS, TIME, and DRC_CONSTRAINT::TIME_DOMAIN.

Referenced by runInternal().

◆ checkStubLengths()

|

private |

Definition at line 723 of file drc_test_provider_matched_length.cpp.

References _, chainTopologyFor(), DRC_ITEM::Create(), DISTANCE, DRCE_NET_CHAIN_STUB_TOO_LONG, NETINFO_ITEM::GetNetChain(), BOARD_CONNECTED_ITEM::GetNetCode(), NETINFO_ITEM::GetNetname(), DRC_CONSTRAINT::GetOption(), NETINFO_ITEM::GetTerminalPad(), DRC_CONSTRAINT::GetValue(), m_board, UNITS_PROVIDER::MessageTextFromValue(), DRC_TEST_PROVIDER::reportViolation(), TIME, DRC_CONSTRAINT::TIME_DOMAIN, and UNDEFINED_LAYER.

Referenced by runInternal().

◆ checkViaCounts()

|

private |

Definition at line 302 of file drc_test_provider_matched_length.cpp.

References _, DRC_ITEM::Create(), DRCE_VIA_COUNT_OUT_OF_RANGE, DRC_CONSTRAINT::GetName(), DRC_CONSTRAINT::GetParentRule(), DRC_CONSTRAINT::GetValue(), MINOPTMAX< T >::HasMax(), MINOPTMAX< T >::HasMin(), MINOPTMAX< T >::Max(), MINOPTMAX< T >::Min(), and DRC_TEST_PROVIDER::reportViolation().

Referenced by runInternal().

◆ forEachGeometryItem()

|

protectedinherited |

Definition at line 159 of file drc_test_provider.cpp.

References BaseType(), BOARD::Drawings(), BOARD::Footprints(), m_drcEngine, MAX_STRUCT_TYPE_ID, pad, PCB_ARC_T, PCB_BARCODE_T, PCB_DIMENSION_T, PCB_FIELD_T, PCB_FOOTPRINT_T, PCB_PAD_T, PCB_SHAPE_T, PCB_TABLE_T, PCB_TABLECELL_T, PCB_TARGET_T, PCB_TEXT_T, PCB_TEXTBOX_T, PCB_TRACE_T, PCB_VIA_T, PCB_ZONE_T, BOARD::Tracks(), and BOARD::Zones().

Referenced by DRC_TEST_PROVIDER_SOLDER_MASK::buildRTrees(), DRC_CACHE_GENERATOR::Run(), DRC_TEST_PROVIDER_DISALLOW::Run(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::Run(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TEXT_MIRRORING::Run(), test::DRC_TEST_PROVIDER_DIFF_PAIR_COUPLING::Run(), DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal(), DRC_TEST_PROVIDER_MISC::testAssertions(), DRC_TEST_PROVIDER_MISC::testDisabledLayers(), DRC_TEST_PROVIDER_SOLDER_MASK::testMaskBridges(), DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance(), and DRC_TEST_PROVIDER_MISC::testTextVars().

◆ formatMsg() [1/2]

|

protectedinherited |

Definition at line 404 of file drc_test_provider.cpp.

References UNITS_PROVIDER::MessageTextFromValue(), and UNITS_PROVIDER::StringFromValue().

◆ formatMsg() [2/2]

|

protectedinherited |

Definition at line 388 of file drc_test_provider.cpp.

References UNITS_PROVIDER::MessageTextFromValue(), and UNITS_PROVIDER::StringFromValue().

Referenced by DRC_TEST_PROVIDER_MATCHED_LENGTH::checkLengths(), DRC_TEST_PROVIDER_HOLE_SIZE::checkPadHole(), DRC_TEST_PROVIDER_HOLE_SIZE::checkViaHole(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::resolveSilkDisposition(), DRC_TEST_PROVIDER_ANNULAR_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TRACK_ANGLE::Run(), DRC_TEST_PROVIDER_TRACK_SEGMENT_LENGTH::Run(), DRC_TEST_PROVIDER_TRACK_WIDTH::Run(), DRC_TEST_PROVIDER_VIA_DIAMETER::Run(), test::DRC_TEST_PROVIDER_DIFF_PAIR_COUPLING::Run(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::testAgainstEdge(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), DRC_TEST_PROVIDER_CREEPAGE::testCreepage(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::testHoleAgainstHole(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstItem(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testItemAgainstZone(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstZones(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testKnockoutTextAgainstZone(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testShapeLineChain(), DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testSingleLayerItemAgainstItem(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testZoneLayer(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testZonesToZones().

◆ GetIuScale()

|

inlineinherited |

Definition at line 55 of file units_provider.h.

References m_iuScale.

Referenced by AngleValueFromString(), GRID_MENU::BuildChoiceList(), RC_ITEM::GetJsonViolation(), DRC_ENGINE::loadImplicitRules(), MessageTextFromMinOptMax(), MessageTextFromValue(), MARGIN_OFFSET_BINDER::onUnitsChanged(), UNIT_BINDER::onUnitsChanged(), OptionalValueFromString(), StringFromOptionalValue(), StringFromValue(), GRID::UserUnitsMessageText(), and ValueFromString().

◆ getLogReporter()

|

inlineprotectedinherited |

Definition at line 136 of file drc_test_provider.h.

References m_drcEngine.

Referenced by DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal().

◆ GetName()

|

inlineoverridevirtual |

Reimplemented from DRC_TEST_PROVIDER.

Definition at line 61 of file drc_test_provider_matched_length.cpp.

◆ GetOriginTransforms()

|

inlinevirtualinherited |

Reimplemented in EDA_BASE_FRAME, and PCB_BASE_FRAME.

Definition at line 58 of file units_provider.h.

◆ GetTypeFromUnits()

|

inlinestaticinherited |

Gets the inferred type from the given units.

Note: will always return the most simple type (e.g. a DISTANCE rather than AREA or VOLUME for a measurement unit).

Definition at line 228 of file units_provider.h.

References CM, DEGREES, DISTANCE, FS, INCH, LENGTH_DELAY, MILS, MM, PERCENT, PS, PS_PER_CM, PS_PER_INCH, PS_PER_MM, TIME, UM, UNITLESS, and UNSCALED.

Referenced by DRC_RULES_PARSER::parseConstraint(), and WX_GRID::SetAutoEvalColUnits().

◆ GetUnitPair()

|

inlinevirtualinherited |

Reimplemented in EDA_DRAW_FRAME.

Definition at line 48 of file units_provider.h.

References GetUserUnits(), EDA_UNIT_UTILS::IsImperialUnit(), MILS, and MM.

◆ GetUnitsFromType()

|

inlineinherited |

Gets the units to use in the conversion based on the underlying user units.

Definition at line 206 of file units_provider.h.

References GetUserUnits(), EDA_UNIT_UTILS::IsMetricUnit(), LENGTH_DELAY, PS, PS_PER_CM, PS_PER_INCH, and TIME.

Referenced by PANEL_SETUP_TUNING_PROFILE_INFO::initPanel(), MessageTextFromMinOptMax(), MessageTextFromValue(), OptionalValueFromString(), StringFromOptionalValue(), StringFromValue(), and ValueFromString().

◆ GetUserUnits()

|

inlineinherited |

Definition at line 45 of file units_provider.h.

References m_userUnits.

Referenced by DIALOG_SHIM::DIALOG_SHIM(), PL_EDITOR_FRAME::DisplayGridMsg(), EDA_DRAW_FRAME::DisplayUnitsMsg(), FOOTPRINT_PREVIEW_PANEL::FOOTPRINT_PREVIEW_PANEL(), FOOTPRINT_WIZARD_FRAME::FOOTPRINT_WIZARD_FRAME(), WX_GRID::getColumnUnits(), RC_ITEM::GetJsonViolation(), GERBER_DRAW_ITEM::GetMsgPanelInfo(), EDA_DRAW_FRAME::GetUnitPair(), GetUnitPair(), GetUnitsFromType(), IfaceOrAddress(), PCB_VIEWER_TOOLS::MeasureTool(), PCB_POINT_EDITOR::OnSelectionChange(), MARGIN_OFFSET_BINDER::onUnitsChanged(), PANEL_PREVIEW_3D_MODEL::onUnitsChanged(), UNIT_BINDER::onUnitsChanged(), POSITION_RELATIVE_TOOL::PositionRelative(), EDA_DRAW_FRAME::SaveSettings(), SCH_EDIT_FRAME::SaveSettings(), PCB_BASE_FRAME::SetBoard(), WX_GRID::SetUnitsProvider(), EDA_DRAW_FRAME::ToggleUserUnits(), EDA_DRAW_FRAME::unitsChangeRefresh(), PCB_BASE_FRAME::unitsChangeRefresh(), EDITOR_CONDITIONS::unitsFunc(), GERBVIEW_FRAME::updateDCodeSelectBox(), PL_EDITOR_FRAME::UpdateStatusBar(), PCB_EDIT_FRAME::UpdateViaSizeSelectBox(), and GRID::UserUnitsMessageText().

◆ Init()

|

staticinherited |

Definition at line 63 of file drc_test_provider.cpp.

References MAX_STRUCT_TYPE_ID, PCB_FOOTPRINT_T, PCB_GROUP_T, PCB_ZONE_T, s_allBasicItems, and s_allBasicItemsButZones.

Referenced by DRC_ENGINE::RunTests().

◆ isInvisibleText()

|

protectedinherited |

Definition at line 376 of file drc_test_provider.cpp.

Referenced by DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), and DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance().

◆ MessageTextFromMinOptMax()

|

inlineinherited |

Definition at line 148 of file units_provider.h.

References DISTANCE, GetIuScale(), GetUnitsFromType(), and EDA_UNIT_UTILS::UI::MessageTextFromMinOptMax().

Referenced by PCB_TRACK::GetMsgPanelInfo(), and PCB_TUNING_PATTERN::GetMsgPanelInfo().

◆ MessageTextFromUnscaledValue()

|

inlineinherited |

Definition at line 141 of file units_provider.h.

References DISTANCE, EDA_UNIT_UTILS::UI::MessageTextFromValue(), unityScale, and UNSCALED.

Referenced by DRC_ENGINE::EvalRules().

◆ MessageTextFromValue() [1/2]

|

inlineinherited |

Definition at line 134 of file units_provider.h.

References EDA_ANGLE::AsDegrees(), DEGREES, DISTANCE, EDA_UNIT_UTILS::UI::MessageTextFromValue(), and unityScale.

◆ MessageTextFromValue() [2/2]

|

inlineinherited |

A lower-precision version of StringFromValue().

Should ONLY be used for status text and messages. Not suitable for dialogs, files, etc. where the loss of precision matters.

Definition at line 127 of file units_provider.h.

References DISTANCE, GetIuScale(), GetUnitsFromType(), and EDA_UNIT_UTILS::UI::MessageTextFromValue().

Referenced by Build_Board_Characteristics_Table(), CheckDuplicatePins(), CheckLibSymbol(), CheckLibSymbolGraphics(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkSkews(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkStubLengths(), GERBVIEW_FRAME::DisplayGridMsg(), GERBER_FILE_IMAGE::DisplayImageInfo(), DRC_ENGINE::EvalRules(), FormatBoardStatisticsJson(), FormatBoardStatisticsReport(), DRC_TEST_PROVIDER::formatMsg(), DRC_TEST_PROVIDER::formatMsg(), DS_DRAW_ITEM_LINE::GetItemDescription(), DS_DRAW_ITEM_RECT::GetItemDescription(), PCB_TRACK::GetItemDescription(), SCH_LINE::GetItemDescription(), SCH_SHAPE::GetItemDescription(), DS_DRAW_ITEM_BASE::GetMsgPanelInfo(), NETINFO_ITEM::GetMsgPanelInfo(), PAD::GetMsgPanelInfo(), PCB_BARCODE::GetMsgPanelInfo(), PCB_DIM_ALIGNED::GetMsgPanelInfo(), PCB_DIM_LEADER::GetMsgPanelInfo(), PCB_DIMENSION_BASE::GetMsgPanelInfo(), PCB_POINT::GetMsgPanelInfo(), PCB_REFERENCE_IMAGE::GetMsgPanelInfo(), PCB_TABLECELL::GetMsgPanelInfo(), PCB_TARGET::GetMsgPanelInfo(), PCB_TEXT::GetMsgPanelInfo(), PCB_TEXTBOX::GetMsgPanelInfo(), PCB_TRACK::GetMsgPanelInfo(), PCB_TUNING_PATTERN::GetMsgPanelInfo(), PCB_VIA::GetMsgPanelInfo(), SCH_BITMAP::GetMsgPanelInfo(), SCH_FIELD::GetMsgPanelInfo(), SCH_JUNCTION::GetMsgPanelInfo(), SCH_LABEL_BASE::GetMsgPanelInfo(), SCH_PIN::GetMsgPanelInfo(), SCH_TABLECELL::GetMsgPanelInfo(), SCH_TEXT::GetMsgPanelInfo(), SCH_TEXTBOX::GetMsgPanelInfo(), STROKE_PARAMS::GetMsgPanelInfo(), ZONE::GetMsgPanelInfo(), GetNetNavigatorItemText(), PCB_TUNING_PATTERN::GetPreviewItems(), PCB_BASE_FRAME::MessageTextFromCoord(), test::DRC_TEST_PROVIDER_DIFF_PAIR_COUPLING::Run(), DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal(), EDA_SHAPE::ShapeGetMsgPanelInfo(), showCoord(), DRC_TEST_PROVIDER_MISC::testOutline(), VIA_SIZE_MENU::update(), PL_EDITOR_FRAME::UpdateMsgPanelInfo(), GERBVIEW_FRAME::UpdateStatusBar(), PCB_BASE_FRAME::UpdateStatusBar(), and SCH_BASE_FRAME::UpdateStatusBar().

◆ OptionalValueFromString()

|

inlineinherited |

Converts aTextValue in aUnits to internal units used by the frame.

Allows the return of an empty optional if the string represents a null value (currently empty string)

- Warning

- This utilizes the current locale and will break if decimal formats differ

- Parameters

-

aType is the type of this value, and controls the way the string is converted to a value aTextValue A reference to a wxString object containing the string to convert.

- Returns

- internal units value

Definition at line 182 of file units_provider.h.

References DISTANCE, EDA_UNIT_UTILS::UI::DoubleValueFromString(), GetIuScale(), GetUnitsFromType(), KiROUND(), and NullUiString.

Referenced by WX_GRID::GetOptionalUnitValue(), and WX_GRID::onCellEditorHidden().

◆ reportPhase()

|

protectedvirtualinherited |

Definition at line 152 of file drc_test_provider.cpp.

References m_drcEngine, and REPORT_AUX.

Referenced by DRC_CACHE_GENERATOR::Run(), DRC_TEST_PROVIDER_ANNULAR_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTIVITY::Run(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::Run(), DRC_TEST_PROVIDER_CREEPAGE::Run(), DRC_TEST_PROVIDER_DISALLOW::Run(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_FOOTPRINT_CHECKS::Run(), DRC_TEST_PROVIDER_HOLE_SIZE::Run(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::Run(), DRC_TEST_PROVIDER_LIBRARY_PARITY::Run(), DRC_TEST_PROVIDER_MISC::Run(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::Run(), DRC_TEST_PROVIDER_SCHEMATIC_PARITY::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_SOLDER_MASK::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TEXT_MIRRORING::Run(), DRC_TEST_PROVIDER_TRACK_ANGLE::Run(), DRC_TEST_PROVIDER_TRACK_SEGMENT_LENGTH::Run(), DRC_TEST_PROVIDER_TRACK_WIDTH::Run(), DRC_TEST_PROVIDER_VIA_DIAMETER::Run(), DRC_TEST_PROVIDER_ZONE_CONNECTIONS::Run(), DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), and DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testFootprintCourtyardDefinitions().

◆ reportProgress()

|

protectedvirtualinherited |

Definition at line 140 of file drc_test_provider.cpp.

References m_drcEngine.

Referenced by DRC_TEST_PROVIDER_SOLDER_MASK::buildRTrees(), DRC_CACHE_GENERATOR::Run(), DRC_TEST_PROVIDER_ANNULAR_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTIVITY::Run(), DRC_TEST_PROVIDER_DISALLOW::Run(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::Run(), DRC_TEST_PROVIDER_LIBRARY_PARITY::Run(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TEXT_MIRRORING::Run(), DRC_TEST_PROVIDER_TRACK_ANGLE::Run(), DRC_TEST_PROVIDER_TRACK_SEGMENT_LENGTH::Run(), DRC_TEST_PROVIDER_TRACK_WIDTH::Run(), DRC_TEST_PROVIDER_VIA_DIAMETER::Run(), DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal(), DRC_TEST_PROVIDER_MISC::testAssertions(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), DRC_TEST_PROVIDER_MISC::testDisabledLayers(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testFootprintCourtyardDefinitions(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadClearances(), DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance(), DRC_TEST_PROVIDER_MISC::testTextVars(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testTrackClearances(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testZonesToZones().

◆ reportTwoItemGeometry()

|

protectedinherited |

Definition at line 129 of file drc_test_provider.cpp.

References BOARD_ITEM::GetEffectiveShape(), and reportTwoShapeGeometry().

Referenced by DRC_TEST_PROVIDER_EDGE_CLEARANCE::testAgainstEdge(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testItemAgainstZone(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstZones(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testKnockoutTextAgainstZone(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testZonesToZones().

◆ reportTwoPointGeometry()

|

protectedinherited |

Definition at line 93 of file drc_test_provider.cpp.

References reportViolation(), SEGMENT, EDA_SHAPE::SetEnd(), PCB_MARKER::SetPath(), and EDA_SHAPE::SetStart().

Referenced by DRC_TEST_PROVIDER_HOLE_SIZE::checkPadHole(), DRC_TEST_PROVIDER_HOLE_SIZE::checkViaHole(), reportTwoShapeGeometry(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::resolveSilkDisposition(), DRC_TEST_PROVIDER_ANNULAR_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::Run(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::testHoleAgainstHole(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testSingleLayerItemAgainstItem().

◆ reportTwoShapeGeometry()

|

protectedinherited |

Definition at line 108 of file drc_test_provider.cpp.

References SHAPE::NearestPoints(), reportTwoPointGeometry(), and reportViolation().

Referenced by reportTwoItemGeometry(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::testHoleAgainstHole(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstItem(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testItemAgainstZone(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstZones(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testSingleLayerItemAgainstItem().

◆ reportViolation()

|

protectedinherited |

Definition at line 84 of file drc_test_provider.cpp.

References m_drcEngine.

Referenced by DRC_TEST_PROVIDER_MATCHED_LENGTH::checkLengths(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkReturnPath(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkSkews(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkStubLengths(), DRC_TEST_PROVIDER_MATCHED_LENGTH::checkViaCounts(), reportTwoPointGeometry(), reportTwoShapeGeometry(), DRC_TEST_PROVIDER_CONNECTIVITY::Run(), DRC_TEST_PROVIDER_DISALLOW::Run(), DRC_TEST_PROVIDER_FOOTPRINT_CHECKS::Run(), DRC_TEST_PROVIDER_LIBRARY_PARITY::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TEXT_MIRRORING::Run(), DRC_TEST_PROVIDER_TRACK_ANGLE::Run(), DRC_TEST_PROVIDER_TRACK_SEGMENT_LENGTH::Run(), DRC_TEST_PROVIDER_TRACK_WIDTH::Run(), DRC_TEST_PROVIDER_VIA_DIAMETER::Run(), test::DRC_TEST_PROVIDER_DIFF_PAIR_COUPLING::Run(), DRC_TEST_PROVIDER_MISC::testAssertions(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), DRC_TEST_PROVIDER_CREEPAGE::testCreepage(), DRC_TEST_PROVIDER_MISC::testDisabledLayers(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testFootprintCourtyardDefinitions(), DRC_TEST_PROVIDER_SOLDER_MASK::testItemAgainstItems(), DRC_TEST_PROVIDER_SOLDER_MASK::testMaskItemAgainstZones(), DRC_TEST_PROVIDER_MISC::testMissingTuningProfiles(), DRC_TEST_PROVIDER_SCHEMATIC_PARITY::testNetlist(), DRC_TEST_PROVIDER_MISC::testOutline(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testShapeLineChain(), DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance(), DRC_TEST_PROVIDER_MISC::testTextVars(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testZoneLayer(), DRC_TEST_PROVIDER_ZONE_CONNECTIONS::testZoneLayer(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testZonesToZones().

◆ Run()

|

overridevirtual |

Run this provider against the given PCB with configured options (if any).

Implements DRC_TEST_PROVIDER.

Definition at line 343 of file drc_test_provider_matched_length.cpp.

References runInternal().

◆ runInternal()

|

private |

Definition at line 349 of file drc_test_provider_matched_length.cpp.

References _, LSET::AllCuMask(), BoardChainBridging(), chainTopologyFor(), checkLengths(), checkReturnPath(), checkSkews(), checkStubLengths(), checkViaCounts(), DRC_RULE::FindConstraint(), DRC_TEST_PROVIDER::forEachGeometryItem(), DRC_LENGTH_REPORT::ENTRY::from, DRC_LENGTH_REPORT::ENTRY::fromItem, DRC_TEST_PROVIDER::getLogReporter(), DRC_CONSTRAINT::GetParentRule(), DRC_CONSTRAINT::IsNull(), DRC_LENGTH_REPORT::ENTRY::items, LENGTH_CONSTRAINT, m_board, m_chainTopoCache, DRC_TEST_PROVIDER::m_drcEngine, m_refUnionCache, m_report, DRC_LENGTH_REPORT::ENTRY::matchingRule, UNITS_PROVIDER::MessageTextFromValue(), NET_CHAIN_LENGTH_CONSTRAINT, NET_CHAIN_RETURN_PATH_CONSTRAINT, NET_CHAIN_STUB_LENGTH_CONSTRAINT, DRC_LENGTH_REPORT::ENTRY::netcode, DRC_LENGTH_REPORT::ENTRY::netinfo, DRC_LENGTH_REPORT::ENTRY::netname, NO_LAYER_DETAIL, LENGTH_DELAY_STATS::NumVias, LENGTH_DELAY_STATS::PadToDieDelay, LENGTH_DELAY_STATS::PadToDieLength, PCB_ARC_T, PCB_PAD_T, PCB_TRACE_T, PCB_VIA_T, REPORT_AUX, DRC_TEST_PROVIDER::reportPhase(), DRC_TEST_PROVIDER::reportProgress(), RPT_SEVERITY_IGNORE, SKEW_CONSTRAINT, DRC_LENGTH_REPORT::ENTRY::to, DRC_LENGTH_REPORT::ENTRY::toItem, DRC_LENGTH_REPORT::ENTRY::total, DRC_LENGTH_REPORT::ENTRY::totalDelay, DRC_LENGTH_REPORT::ENTRY::totalPadToDie, DRC_LENGTH_REPORT::ENTRY::totalPadToDieDelay, DRC_LENGTH_REPORT::ENTRY::totalRoute, DRC_LENGTH_REPORT::ENTRY::totalRouteDelay, DRC_LENGTH_REPORT::ENTRY::totalVia, DRC_LENGTH_REPORT::ENTRY::totalViaDelay, LENGTH_DELAY_STATS::TrackDelay, LENGTH_DELAY_STATS::TrackLength, LENGTH_DELAY_CALCULATION_ITEM::Type(), VIA_COUNT_CONSTRAINT, DRC_LENGTH_REPORT::ENTRY::viaCount, LENGTH_DELAY_STATS::ViaDelay, LENGTH_DELAY_STATS::ViaLength, and WITH_DELAY_DETAIL.

Referenced by Run().

◆ RunTests()

|

inlineinherited |

Definition at line 119 of file drc_test_provider.h.

References Run(), and UNITS_PROVIDER::SetUserUnits().

◆ SetDRCEngine()

|

inlineinherited |

Definition at line 114 of file drc_test_provider.h.

References m_drcEngine.

Referenced by DRC_INTERACTIVE_COURTYARD_CLEARANCE::DRC_INTERACTIVE_COURTYARD_CLEARANCE(), and DRC_ENGINE::RunTests().

◆ SetUserUnits()

|

inlineinherited |

Definition at line 46 of file units_provider.h.

References m_userUnits.

Referenced by EDA_BASE_FRAME::ChangeUserUnits(), EDA_DRAW_FRAME::EDA_DRAW_FRAME(), FOOTPRINT_WIZARD_FRAME::FOOTPRINT_WIZARD_FRAME(), PCB_DIM_ALIGNED::GetMsgPanelInfo(), PCB_DIMENSION_BASE::GetMsgPanelInfo(), IfaceOrAddress(), EDA_DRAW_FRAME::LoadSettings(), PL_EDITOR_FRAME::PL_EDITOR_FRAME(), DRC_ENGINE::RunTests(), DRC_TEST_PROVIDER::RunTests(), and EDA_DRAW_FRAME::ToggleUserUnits().

◆ StringFromOptionalValue()

|

inlineinherited |

Converts an optional aValue in internal units into a united string.

For readability, trailing 0s are removed if the mantissa has 3 or more digits. This function should be used to display values in dialogs because a value entered in mm (for instance 2.0 mm) could need up to 8 digits mantissa if displayed in inch to avoid truncation or rounding made just by the printf function.

- Parameters

-

aValue = optional value in internal units aAddUnitLabel = true to add symbol unit to the string value aType is the type of this value, and controls the way the value is converted to a string, and the suitable unit

- Returns

- A wxString object containing value and optionally the symbol unit (like 2.000 mm)

Definition at line 100 of file units_provider.h.

References DISTANCE, GetIuScale(), GetUnitsFromType(), NullUiString, and EDA_UNIT_UTILS::UI::StringFromValue().

Referenced by WX_GRID::onCellEditorHidden().

◆ StringFromValue() [1/2]

|

inlineinherited |

Definition at line 114 of file units_provider.h.

References EDA_ANGLE::AsDegrees(), DEGREES, DISTANCE, EDA_UNIT_UTILS::UI::StringFromValue(), and unityScale.

◆ StringFromValue() [2/2]

|

inlineinherited |

Converts aValue in internal units into a united string.

For readability, trailing 0s are removed if the mantissa has 3 or more digits. This function should be used to display values in dialogs because a value entered in mm (for instance 2.0 mm) could need up to 8 digits mantissa if displayed in inch to avoid truncation or rounding made just by the printf function.

- Parameters

-

aValue = value in internal units aAddUnitLabel = true to add symbol unit to the string value aType is the type of this value, and controls the way the value is converted to a string, and the suitable unit

- Returns

- A wxString object containing value and optionally the symbol unit (like 2.000 mm)

Definition at line 79 of file units_provider.h.

References DISTANCE, GetIuScale(), GetUnitsFromType(), and EDA_UNIT_UTILS::UI::StringFromValue().

Referenced by Build_Board_Stackup_Table(), MICROWAVE_TOOL::createFootprint(), MICROWAVE_TOOL::createMicrowaveInductor(), PAD::doCheckPad(), VALIDATION_ERROR_TOO_LARGE< T >::Format(), VALIDATION_ERROR_TOO_SMALL< T >::Format(), formatBBox(), DRC_TEST_PROVIDER::formatMsg(), DRC_TEST_PROVIDER::formatMsg(), WX_GRID::onCellEditorHidden(), reportMax(), reportMin(), reportOpt(), and PANEL_SETUP_TEXT_AND_GRAPHICS::TransferDataFromWindow().

◆ ValueFromString()

|

inlineinherited |

Converts aTextValue in aUnits to internal units used by the frame.

- Warning

- This utilizes the current locale and will break if decimal formats differ

- Parameters

-

aType is the type of this value, and controls the way the string is converted to a value aTextValue A reference to a wxString object containing the string to convert.

- Returns

- internal units value

Definition at line 163 of file units_provider.h.

References DISTANCE, EDA_UNIT_UTILS::UI::DoubleValueFromString(), GetIuScale(), GetUnitsFromType(), and KiROUND().

Referenced by PIN_TABLE_DATA_MODEL::compare(), MICROWAVE_TOOL::createFootprint(), MICROWAVE_TOOL::createMicrowaveInductor(), WX_GRID::GetUnitValue(), and WX_GRID::onCellEditorHidden().

◆ zoneUnionFor()

|

private |

Definition at line 678 of file drc_test_provider_matched_length.cpp.

References SHAPE_POLY_SET::BooleanAdd(), m_board, m_refUnionCache, SHAPE_POLY_SET::OutlineCount(), SHAPE_POLY_SET::Simplify(), and WildCompareString().

Referenced by checkReturnPath().

Member Data Documentation

◆ m_board

|

private |

Definition at line 95 of file drc_test_provider_matched_length.cpp.

Referenced by chainTopologyFor(), checkReturnPath(), checkSkews(), checkStubLengths(), DRC_TEST_PROVIDER_MATCHED_LENGTH(), runInternal(), and zoneUnionFor().

◆ m_chainTopoCache

|

private |

Definition at line 97 of file drc_test_provider_matched_length.cpp.

Referenced by chainTopologyFor(), and runInternal().

◆ m_drcEngine

|

protectedinherited |

Definition at line 170 of file drc_test_provider.h.

Referenced by DRC_TEST_PROVIDER_HOLE_SIZE::checkPadHole(), DRC_TEST_PROVIDER_HOLE_SIZE::checkViaHole(), DRC_TEST_PROVIDER(), forEachGeometryItem(), getLogReporter(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::layerDesc(), DRC_TEST_PROVIDER_SLIVER_CHECKER::layerDesc(), reportPhase(), reportProgress(), reportViolation(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::resolveSilkDisposition(), DRC_CACHE_GENERATOR::Run(), DRC_INTERACTIVE_COURTYARD_CLEARANCE::Run(), DRC_TEST_PROVIDER_ANNULAR_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTION_WIDTH::Run(), DRC_TEST_PROVIDER_CONNECTIVITY::Run(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::Run(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::Run(), DRC_TEST_PROVIDER_CREEPAGE::Run(), DRC_TEST_PROVIDER_DISALLOW::Run(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_FOOTPRINT_CHECKS::Run(), DRC_TEST_PROVIDER_HOLE_SIZE::Run(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::Run(), DRC_TEST_PROVIDER_LIBRARY_PARITY::Run(), DRC_TEST_PROVIDER_MISC::Run(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::Run(), DRC_TEST_PROVIDER_SCHEMATIC_PARITY::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_SOLDER_MASK::Run(), DRC_TEST_PROVIDER_TEXT_DIMS::Run(), DRC_TEST_PROVIDER_TEXT_MIRRORING::Run(), DRC_TEST_PROVIDER_TRACK_ANGLE::Run(), DRC_TEST_PROVIDER_TRACK_SEGMENT_LENGTH::Run(), DRC_TEST_PROVIDER_TRACK_WIDTH::Run(), DRC_TEST_PROVIDER_VIA_DIAMETER::Run(), DRC_TEST_PROVIDER_ZONE_CONNECTIONS::Run(), test::DRC_TEST_PROVIDER_DIFF_PAIR_COUPLING::Run(), DRC_TEST_PROVIDER_MATCHED_LENGTH::runInternal(), SetDRCEngine(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::testAgainstEdge(), DRC_TEST_PROVIDER_MISC::testAssertions(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testCourtyardClearances(), DRC_TEST_PROVIDER_CREEPAGE::testCreepage(), DRC_TEST_PROVIDER_MISC::testDisabledLayers(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::testFootprintCourtyardDefinitions(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testGraphicClearances(), DRC_TEST_PROVIDER_HOLE_TO_HOLE::testHoleAgainstHole(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstItem(), DRC_TEST_PROVIDER_SOLDER_MASK::testItemAgainstItems(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testItemAgainstZone(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testItemAgainstZones(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testKnockoutTextAgainstZone(), DRC_TEST_PROVIDER_SOLDER_MASK::testMaskItemAgainstZones(), DRC_TEST_PROVIDER_MISC::testMissingTuningProfiles(), DRC_TEST_PROVIDER_SCHEMATIC_PARITY::testNetlist(), DRC_TEST_PROVIDER_MISC::testOutline(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadAgainstItem(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testPadClearances(), DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testSingleLayerItemAgainstItem(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testTeardropClearances(), DRC_TEST_PROVIDER_MISC::testTextVars(), DRC_TEST_PROVIDER_COPPER_CLEARANCE::testTrackClearances(), DRC_TEST_PROVIDER_PHYSICAL_CLEARANCE::testZoneLayer(), DRC_TEST_PROVIDER_ZONE_CONNECTIONS::testZoneLayer(), and DRC_TEST_PROVIDER_COPPER_CLEARANCE::testZonesToZones().

◆ m_isRuleDriven

|

protectedinherited |

Definition at line 172 of file drc_test_provider.h.

Referenced by DRC_INTERACTIVE_COURTYARD_CLEARANCE::DRC_INTERACTIVE_COURTYARD_CLEARANCE(), DRC_TEST_PROVIDER_COURTYARD_CLEARANCE::DRC_TEST_PROVIDER_COURTYARD_CLEARANCE(), DRC_TEST_PROVIDER_FOOTPRINT_CHECKS::DRC_TEST_PROVIDER_FOOTPRINT_CHECKS(), DRC_TEST_PROVIDER_LIBRARY_PARITY::DRC_TEST_PROVIDER_LIBRARY_PARITY(), DRC_TEST_PROVIDER_MISC::DRC_TEST_PROVIDER_MISC(), and DRC_TEST_PROVIDER_SCHEMATIC_PARITY::DRC_TEST_PROVIDER_SCHEMATIC_PARITY().

◆ m_iuScale

|

privateinherited |

Definition at line 260 of file units_provider.h.

Referenced by GetIuScale(), and UNITS_PROVIDER().

◆ m_refUnionCache

|

private |

Definition at line 98 of file drc_test_provider_matched_length.cpp.

Referenced by runInternal(), and zoneUnionFor().

◆ m_report

|

private |

Definition at line 96 of file drc_test_provider_matched_length.cpp.

Referenced by runInternal().

◆ m_userUnits

|

privateinherited |

Definition at line 261 of file units_provider.h.

Referenced by GetUserUnits(), SetUserUnits(), and UNITS_PROVIDER().

◆ NullUiString

|

inlinestaticinherited |

The string that is used in the UI to represent a null value.

Definition at line 257 of file units_provider.h.

Referenced by WX_GRID::GetOptionalUnitValue(), WX_GRID::onCellEditorHidden(), OptionalValueFromString(), and StringFromOptionalValue().

◆ s_allBasicItems

|

staticprotectedinherited |

Definition at line 166 of file drc_test_provider.h.

Referenced by DRC_TEST_PROVIDER_SOLDER_MASK::buildRTrees(), Init(), DRC_TEST_PROVIDER_EDGE_CLEARANCE::Run(), DRC_TEST_PROVIDER_SILK_CLEARANCE::Run(), DRC_TEST_PROVIDER_SLIVER_CHECKER::Run(), DRC_TEST_PROVIDER_MISC::testDisabledLayers(), and DRC_TEST_PROVIDER_SOLDER_MASK::testSilkToMaskClearance().

◆ s_allBasicItemsButZones

|

staticprotectedinherited |

Definition at line 167 of file drc_test_provider.h.

Referenced by Init(), and DRC_TEST_PROVIDER_SOLDER_MASK::testMaskBridges().

The documentation for this class was generated from the following file: