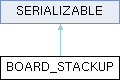

Manage layers needed to make a physical board. More...

#include <board_stackup.h>

Public Member Functions | |

| BOARD_STACKUP () | |

| BOARD_STACKUP (const BOARD_STACKUP &aOther) | |

| BOARD_STACKUP & | operator= (const BOARD_STACKUP &aOther) |

| bool | operator== (const BOARD_STACKUP &aOther) const |

| bool | operator!= (const BOARD_STACKUP &aOther) const |

| ~BOARD_STACKUP () | |

| void | Serialize (google::protobuf::Any &aContainer) const override |

| Serializes this object to the given Any message. | |

| bool | Deserialize (const google::protobuf::Any &aContainer) override |

| Deserializes the given protobuf message into this object. | |

| const std::vector< BOARD_STACKUP_ITEM * > & | GetList () const |

| BOARD_STACKUP_ITEM * | GetStackupLayer (int aIndex) |

| void | RemoveAll () |

| Delete all items in list and clear the list. | |

| int | GetCount () const |

| int | BuildBoardThicknessFromStackup () const |

| void | Add (BOARD_STACKUP_ITEM *aItem) |

| Add a new item in stackup layer. | |

| bool | SynchronizeWithBoard (BOARD_DESIGN_SETTINGS *aSettings) |

| Synchronize the BOARD_STACKUP_ITEM* list with the board. | |

| void | BuildDefaultStackupList (const BOARD_DESIGN_SETTINGS *aSettings, int aActiveCopperLayersCount=0) |

| Create a default stackup, according to the current BOARD_DESIGN_SETTINGS settings. | |

| void | FormatBoardStackup (OUTPUTFORMATTER *aFormatter, const BOARD *aBoard) const |

| Write the stackup info on board file. | |

| int | GetLayerDistance (PCB_LAYER_ID aFirstLayer, PCB_LAYER_ID aSecondLayer) const |

| Calculate the distance (height) between the two given copper layers. | |

Static Public Member Functions | |

| static LSET | StackupAllowedBrdLayers () |

Public Attributes | |

| wxString | m_FinishType |

| The name of external copper finish. | |

| bool | m_HasDielectricConstrains |

| True if some layers have impedance controlled tracks or have specific constrains for micro-wave applications If the board has dielectric constrains, the .gbrjob will contain info about dielectric constrains: loss tangent and Epsilon rel. | |

| bool | m_HasThicknessConstrains |

| True if some layers (copper and/or dielectric) have specific thickness. | |

| BS_EDGE_CONNECTOR_CONSTRAINTS | m_EdgeConnectorConstraints |

| If the board has edge connector cards, some constrains can be specified in job file: BS_EDGE_CONNECTOR_NONE = no edge connector BS_EDGE_CONNECTOR_IN_USE = board has edge connectors BS_EDGE_CONNECTOR_BEVELLED = edge connectors are beveled. | |

| bool | m_EdgePlating |

| True if the edge board is plated. | |

Private Attributes | |

| std::vector< BOARD_STACKUP_ITEM * > | m_list |

Detailed Description

Manage layers needed to make a physical board.

They are solder mask, silk screen, copper and dielectric. Some other layers, used in fabrication, are not managed here because they are not used to make a physical board itself.

- Note

- There are a few other parameters related to the physical stackup like finish type, impedance control and a few others.

Definition at line 233 of file board_stackup.h.

Constructor & Destructor Documentation

◆ BOARD_STACKUP() [1/2]

| BOARD_STACKUP::BOARD_STACKUP | ( | ) |

Definition at line 392 of file board_stackup.cpp.

References BS_EDGE_CONNECTOR_NONE, m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, and m_HasThicknessConstrains.

Referenced by BOARD_STACKUP(), BuildDefaultStackupList(), operator!=(), operator=(), operator==(), and SynchronizeWithBoard().

◆ BOARD_STACKUP() [2/2]

| BOARD_STACKUP::BOARD_STACKUP | ( | const BOARD_STACKUP & | aOther | ) |

Definition at line 403 of file board_stackup.cpp.

References Add(), BOARD_STACKUP(), m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, m_HasThicknessConstrains, and m_list.

◆ ~BOARD_STACKUP()

|

inline |

Definition at line 243 of file board_stackup.h.

References RemoveAll().

Member Function Documentation

◆ Add()

|

inline |

Add a new item in stackup layer.

Definition at line 275 of file board_stackup.h.

References m_list.

Referenced by BOARD_STACKUP(), BuildDefaultStackupList(), operator=(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), and PANEL_SETUP_BOARD_STACKUP::TransferDataFromWindow().

◆ BuildBoardThicknessFromStackup()

| int BOARD_STACKUP::BuildBoardThicknessFromStackup | ( | ) | const |

- Returns

- the board thickness ( in UI) from the thickness of BOARD_STACKUP_ITEM list

Definition at line 537 of file board_stackup.cpp.

References m_list.

Referenced by ComputeBoardStatistics(), PCB_IO_IPC2581::generateStackup(), PCB_IO_PADS::loadBoardSetup(), CADSTAR_PCB_ARCHIVE_LOADER::loadBoardStackup(), ALTIUM_PCB::ParseBoard6Data(), and PANEL_SETUP_BOARD_STACKUP::TransferDataFromWindow().

◆ BuildDefaultStackupList()

| void BOARD_STACKUP::BuildDefaultStackupList | ( | const BOARD_DESIGN_SETTINGS * | aSettings, |

| int | aActiveCopperLayersCount = 0 ) |

Create a default stackup, according to the current BOARD_DESIGN_SETTINGS settings.

- Parameters

-

aSettings is the current board setting. if nullptr, build a full stackup (with 32 copper layers) aActiveCopperLayersCount is used only if aSettings == nullptr is the number of copper layers to use to calculate a default dielectric thickness. ((<= 0 to use all copper layers)

Definition at line 654 of file board_stackup.cpp.

References _HKI, Add(), B_Cu, B_Mask, B_Paste, B_SilkS, BOARD_STACKUP(), BS_ITEM_TYPE_COPPER, BS_ITEM_TYPE_DIELECTRIC, BS_ITEM_TYPE_SILKSCREEN, BS_ITEM_TYPE_SOLDERMASK, BS_ITEM_TYPE_SOLDERPASTE, LSET::CuStack(), F_Mask, F_Paste, F_SilkS, BOARD_DESIGN_SETTINGS::GetBoardThickness(), BOARD_STACKUP_ITEM::GetCopperDefaultThickness(), BOARD_DESIGN_SETTINGS::GetCopperLayerCount(), BOARD_DESIGN_SETTINGS::GetEnabledLayers(), BOARD_STACKUP_ITEM::GetMaskDefaultThickness(), BOARD_DESIGN_SETTINGS::GetStackupDescriptor(), KEY_COPPER, KEY_CORE, KEY_PREPREG, m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, pcbIUScale, BOARD_STACKUP_ITEM::SetBrdLayerId(), BOARD_STACKUP_ITEM::SetDielectricLayerId(), BOARD_STACKUP_ITEM::SetMaterial(), BOARD_STACKUP_ITEM::SetThickness(), BOARD_STACKUP_ITEM::SetTypeName(), and StackupAllowedBrdLayers().

Referenced by BOOST_AUTO_TEST_CASE(), FOOTPRINT_CHOOSER_FRAME::build3DCanvas(), BOARD::GetStackupOrDefault(), DIALOG_MIGRATE_3D_MODELS::initPreviewBoard(), PCB_IO_PADS::loadBoardSetup(), CADSTAR_PCB_ARCHIVE_LOADER::loadBoardStackup(), PANEL_PREVIEW_3D_MODEL::PANEL_PREVIEW_3D_MODEL(), ALTIUM_PCB::ParseBoard6Data(), PCB_IO_KICAD_SEXPR_PARSER::parseSetup(), BACKDRILL_TEST_FIXTURE::SetupSixLayerBoard(), LENGTH_DELAY_CALCULATION::StackupHeight(), SynchronizeWithBoard(), and PANEL_PREVIEW_3D_MODEL::View3DSettings().

◆ Deserialize()

|

overridevirtual |

Deserializes the given protobuf message into this object.

- Parameters

-

aContainer is an Any which should have a concrete type matching this object

- Returns

- true if unpacking and deserialization succeeded

Reimplemented from SERIALIZABLE.

Definition at line 512 of file board_stackup.cpp.

◆ FormatBoardStackup()

| void BOARD_STACKUP::FormatBoardStackup | ( | OUTPUTFORMATTER * | aFormatter, |

| const BOARD * | aBoard ) const |

Write the stackup info on board file.

- Parameters

-

aFormatter is the OUTPUTFORMATTER used to create the file aBoard is the board

Definition at line 778 of file board_stackup.cpp.

References BS_ITEM_TYPE_DIELECTRIC, DJORDJEVIC_SARKAR, KICAD_FORMAT::FormatBool(), FormatDouble2Str(), EDA_UNIT_UTILS::FormatInternalUnits(), IsPrmSpecified(), m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, m_list, LSET::Name(), pcbIUScale, OUTPUTFORMATTER::Print(), OUTPUTFORMATTER::Quotew(), and UNDEFINED_LAYER.

Referenced by PCB_IO_KICAD_SEXPR::formatSetup(), and PANEL_SETUP_BOARD_STACKUP::TransferDataFromWindow().

◆ GetCount()

|

inline |

- Returns

- the number of layers in the stackup

Definition at line 269 of file board_stackup.h.

References m_list.

Referenced by GERBER_JOBFILE_WRITER::addJSONMaterialStackup(), BOOST_AUTO_TEST_CASE(), Build_Board_Stackup_Table(), PCB_IO_IPC2581::generateCadLayers(), PCB_IO_IPC2581::generateCadSpecs(), PCB_IO_IPC2581::generateStackup(), GetStackupLayer(), ODB_MATRIX_ENTITY::InitMatrixLayerData(), BOARD_ADAPTER::InitSettings(), and PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup().

◆ GetLayerDistance()

| int BOARD_STACKUP::GetLayerDistance | ( | PCB_LAYER_ID | aFirstLayer, |

| PCB_LAYER_ID | aSecondLayer ) const |

Calculate the distance (height) between the two given copper layers.

This factors in the thickness of any dielectric and copper layers between the two given layers, and half the height of the given start and end layers. This half-height calculation allows this to be used for consistent length measurements when calculating net length through a series of vias. A more advanced algorithm would be possible once we have a good concept of the start and end for a length measurement, but for now this will do. See https://gitlab.com/kicad/code/kicad/-/issues/8384 for more background.

- Parameters

-

aFirstLayer is a copper layer aSecondLayer is a different copper layer

- Returns

- the height (in IU) between the two layers

Definition at line 875 of file board_stackup.cpp.

References B_Cu, F_Cu, IsCopperLayer(), m_list, and UNDEFINED_LAYER.

Referenced by GENDRILL_WRITER_BASE::buildHolesList(), PCB_IO_IPC2581::ensureBackdrillSpecs(), PAD::GetPostMachiningKnockout(), PCB_VIA::GetPostMachiningKnockout(), LENGTH_DELAY_CALCULATION::StackupHeight(), and PNS_KICAD_IFACE_BASE::StackupHeight().

◆ GetList()

|

inline |

Definition at line 249 of file board_stackup.h.

References m_list.

Referenced by BOOST_AUTO_TEST_CASE(), Build_Board_Stackup_Table(), PANEL_SETUP_BOARD_STACKUP::buildLayerStackPanel(), BuildStackupReport(), EXPORTER_PCB_VRML::EXPORTER_PCB_VRML(), ODB_LAYER_ENTITY::GenAttrList(), PCB_IO_IPC2581::generateCadLayers(), PCB_IO_IPC2581::generateCadSpecs(), PCB_IO_IPC2581::generateContentStackup(), PCB_IO_IPC2581::generateStackup(), BOARD_ADAPTER::GetLayerColors(), PANEL_SETUP_TUNING_PROFILE_INFO::getMicrostripBoardParameters(), GetStackupLayer(), PANEL_SETUP_TUNING_PROFILE_INFO::getStriplineBoardParameters(), ODB_MATRIX_ENTITY::InitMatrixLayerData(), BOARD_ADAPTER::InitSettings(), PCB_IO_PADS::loadBoardSetup(), CADSTAR_PCB_ARCHIVE_LOADER::loadBoardStackup(), ALTIUM_PCB::ParseBoard6Data(), SynchronizeWithBoard(), and HYPERLYNX_EXPORTER::writeStackupInfo().

◆ GetStackupLayer()

| BOARD_STACKUP_ITEM * BOARD_STACKUP::GetStackupLayer | ( | int | aIndex | ) |

- Returns

- a reference to the layer aIndex, or nullptr if not exists

Definition at line 528 of file board_stackup.cpp.

References GetCount(), and GetList().

Referenced by GERBER_JOBFILE_WRITER::addJSONMaterialStackup().

◆ operator!=()

|

inline |

Definition at line 241 of file board_stackup.h.

References BOARD_STACKUP(), and operator==().

◆ operator=()

| BOARD_STACKUP & BOARD_STACKUP::operator= | ( | const BOARD_STACKUP & | aOther | ) |

Definition at line 421 of file board_stackup.cpp.

References Add(), BOARD_STACKUP(), m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, m_HasThicknessConstrains, m_list, and RemoveAll().

◆ operator==()

| bool BOARD_STACKUP::operator== | ( | const BOARD_STACKUP & | aOther | ) | const |

Definition at line 443 of file board_stackup.cpp.

References BOARD_STACKUP(), m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, m_HasThicknessConstrains, and m_list.

Referenced by operator!=().

◆ RemoveAll()

| void BOARD_STACKUP::RemoveAll | ( | ) |

Delete all items in list and clear the list.

Definition at line 519 of file board_stackup.cpp.

References m_list.

Referenced by FOOTPRINT_CHOOSER_FRAME::build3DCanvas(), DIALOG_MIGRATE_3D_MODELS::initPreviewBoard(), PCB_IO_PADS::loadBoardSetup(), CADSTAR_PCB_ARCHIVE_LOADER::loadBoardStackup(), operator=(), PANEL_PREVIEW_3D_MODEL::PANEL_PREVIEW_3D_MODEL(), ALTIUM_PCB::ParseBoard6Data(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), PCB_IO_KICAD_SEXPR_PARSER::parseSetup(), PANEL_SETUP_BOARD_STACKUP::TransferDataFromWindow(), PANEL_PREVIEW_3D_MODEL::View3DSettings(), and ~BOARD_STACKUP().

◆ Serialize()

|

overridevirtual |

Serializes this object to the given Any message.

The Any message's concrete type will be specific to the object in question.

- Parameters

-

aContainer will be filled with a message describing this object

Reimplemented from SERIALIZABLE.

Definition at line 464 of file board_stackup.cpp.

References BS_ITEM_TYPE_COPPER, BS_ITEM_TYPE_DIELECTRIC, m_list, and ToProtoEnum().

Referenced by API_HANDLER_PCB::handleGetStackup().

◆ StackupAllowedBrdLayers()

|

inlinestatic |

- Returns

- the board layers full mask allowed in the stackup list i.e. the SilkS, Mask, Paste and all copper layers

Definition at line 258 of file board_stackup.h.

References B_Mask, B_Paste, B_SilkS, LSET::ExternalCuMask(), F_Mask, F_Paste, F_SilkS, and LSET::InternalCuMask().

Referenced by BuildDefaultStackupList(), PANEL_SETUP_BOARD_STACKUP::ImportSettingsFrom(), PANEL_SETUP_BOARD_STACKUP::OnLayersOptionsChanged(), and PANEL_SETUP_BOARD_STACKUP::PANEL_SETUP_BOARD_STACKUP().

◆ SynchronizeWithBoard()

| bool BOARD_STACKUP::SynchronizeWithBoard | ( | BOARD_DESIGN_SETTINGS * | aSettings | ) |

Synchronize the BOARD_STACKUP_ITEM* list with the board.

Not enabled layers are removed Missing layers are added

- Parameters

-

aSettings,is the current board setting.

- Returns

- true if changes are made

Definition at line 561 of file board_stackup.cpp.

References BOARD_STACKUP(), BuildDefaultStackupList(), GetList(), BOARD_DESIGN_SETTINGS::GetStackupDescriptor(), m_EdgeConnectorConstraints, m_EdgePlating, m_FinishType, m_HasDielectricConstrains, m_list, and UNDEFINED_LAYER.

Referenced by GERBER_JOBFILE_WRITER::addJSONMaterialStackup(), PCB_CONTROL::AppendBoard(), Build_Board_Characteristics_Table(), Build_Board_Stackup_Table(), PCB_IO_IPC2581::ensureBackdrillSpecs(), PCB_IO_IPC2581::generateCadLayers(), PCB_IO_IPC2581::generateCadSpecs(), PCB_IO_IPC2581::generateContentStackup(), PCB_IO_IPC2581::generateStackup(), and ODB_MATRIX_ENTITY::InitMatrixLayerData().

Member Data Documentation

◆ m_EdgeConnectorConstraints

| BS_EDGE_CONNECTOR_CONSTRAINTS BOARD_STACKUP::m_EdgeConnectorConstraints |

If the board has edge connector cards, some constrains can be specified in job file: BS_EDGE_CONNECTOR_NONE = no edge connector BS_EDGE_CONNECTOR_IN_USE = board has edge connectors BS_EDGE_CONNECTOR_BEVELLED = edge connectors are beveled.

Definition at line 346 of file board_stackup.h.

Referenced by GERBER_JOBFILE_WRITER::addJSONGeneralSpecs(), BOARD_STACKUP(), BOARD_STACKUP(), Build_Board_Characteristics_Table(), BuildDefaultStackupList(), BuildStackupReport(), FormatBoardStackup(), operator=(), operator==(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), SynchronizeWithBoard(), PANEL_SETUP_BOARD_FINISH::synchronizeWithBoard(), and PANEL_SETUP_BOARD_FINISH::TransferDataFromWindow().

◆ m_EdgePlating

| bool BOARD_STACKUP::m_EdgePlating |

True if the edge board is plated.

Definition at line 348 of file board_stackup.h.

Referenced by GERBER_JOBFILE_WRITER::addJSONGeneralSpecs(), BOARD_STACKUP(), BOARD_STACKUP(), Build_Board_Characteristics_Table(), BuildDefaultStackupList(), BuildStackupReport(), FormatBoardStackup(), operator=(), operator==(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), SynchronizeWithBoard(), PANEL_SETUP_BOARD_FINISH::synchronizeWithBoard(), and PANEL_SETUP_BOARD_FINISH::TransferDataFromWindow().

◆ m_FinishType

| wxString BOARD_STACKUP::m_FinishType |

The name of external copper finish.

Definition at line 323 of file board_stackup.h.

Referenced by GERBER_JOBFILE_WRITER::addJSONGeneralSpecs(), BOARD_STACKUP(), BOARD_STACKUP(), BOOST_AUTO_TEST_CASE(), BOOST_AUTO_TEST_CASE(), BOOST_AUTO_TEST_CASE(), Build_Board_Characteristics_Table(), BuildDefaultStackupList(), BuildStackupReport(), EXPORTER_PCB_VRML::EXPORTER_PCB_VRML(), FormatBoardStackup(), PCB_IO_IPC2581::generateCadLayers(), PCB_IO_IPC2581::generateCadSpecs(), PCB_IO_IPC2581::generateStackup(), BOARD_ADAPTER::GetLayerColors(), operator=(), operator==(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), SynchronizeWithBoard(), PANEL_SETUP_BOARD_FINISH::synchronizeWithBoard(), and PANEL_SETUP_BOARD_FINISH::TransferDataFromWindow().

◆ m_HasDielectricConstrains

| bool BOARD_STACKUP::m_HasDielectricConstrains |

True if some layers have impedance controlled tracks or have specific constrains for micro-wave applications If the board has dielectric constrains, the .gbrjob will contain info about dielectric constrains: loss tangent and Epsilon rel.

If not, these values will be not specified in job file.

Definition at line 332 of file board_stackup.h.

Referenced by GERBER_JOBFILE_WRITER::addJSONGeneralSpecs(), GERBER_JOBFILE_WRITER::addJSONMaterialStackup(), BOARD_STACKUP(), BOARD_STACKUP(), Build_Board_Characteristics_Table(), BuildDefaultStackupList(), BuildStackupReport(), FormatBoardStackup(), operator=(), operator==(), PCB_IO_KICAD_SEXPR_PARSER::parseBoardStackup(), SynchronizeWithBoard(), PANEL_SETUP_BOARD_STACKUP::synchronizeWithBoard(), and PANEL_SETUP_BOARD_STACKUP::TransferDataFromWindow().

◆ m_HasThicknessConstrains

| bool BOARD_STACKUP::m_HasThicknessConstrains |

True if some layers (copper and/or dielectric) have specific thickness.

Definition at line 337 of file board_stackup.h.

Referenced by BOARD_STACKUP(), BOARD_STACKUP(), operator=(), and operator==().

◆ m_list

|

private |

Definition at line 353 of file board_stackup.h.

Referenced by Add(), BOARD_STACKUP(), BuildBoardThicknessFromStackup(), FormatBoardStackup(), GetCount(), GetLayerDistance(), GetList(), operator=(), operator==(), RemoveAll(), Serialize(), and SynchronizeWithBoard().

The documentation for this class was generated from the following files: