Public Member Functions | |

| PNS_PCBNEW_RULE_RESOLVER (BOARD *aBoard, PNS::ROUTER_IFACE *aRouterIface) | |

| virtual | ~PNS_PCBNEW_RULE_RESOLVER () |

| int | Clearance (const PNS::ITEM *aA, const PNS::ITEM *aB, bool aUseClearanceEpsilon=true) override |

| PNS::NET_HANDLE | DpCoupledNet (PNS::NET_HANDLE aNet) override |

| int | DpNetPolarity (PNS::NET_HANDLE aNet) override |

| bool | DpNetPair (const PNS::ITEM *aItem, PNS::NET_HANDLE &aNetP, PNS::NET_HANDLE &aNetN) override |

| int | NetCode (PNS::NET_HANDLE aNet) override |

| wxString | NetName (PNS::NET_HANDLE aNet) override |

| bool | IsInNetTie (const PNS::ITEM *aA) override |

| bool | IsNetTieExclusion (const PNS::ITEM *aItem, const VECTOR2I &aCollisionPos, const PNS::ITEM *aCollidingItem) override |

| bool | IsDrilledHole (const PNS::ITEM *aItem) override |

| bool | IsNonPlatedSlot (const PNS::ITEM *aItem) override |

| bool | IsKeepout (const PNS::ITEM *aObstacle, const PNS::ITEM *aItem, bool *aEnforce) override |

| bool | QueryConstraint (PNS::CONSTRAINT_TYPE aType, const PNS::ITEM *aItemA, const PNS::ITEM *aItemB, int aLayer, PNS::CONSTRAINT *aConstraint) override |

| int | ClearanceEpsilon () const override |

| void | ClearCacheForItems (std::vector< const PNS::ITEM * > &aItems) override |

| void | ClearCaches () override |

| void | ClearTemporaryCaches () override |

| const SHAPE_LINE_CHAIN & | HullCache (const PNS::ITEM *aItem, int aClearance, int aWalkaroundThickness, int aLayer) override |

Private Member Functions | |

| BOARD_ITEM * | getBoardItem (const PNS::ITEM *aItem, PCB_LAYER_ID aBoardLayer, int aIdx=0) |

Private Attributes | |

| PNS::ROUTER_IFACE * | m_routerIface |

| BOARD * | m_board |

| PCB_TRACK | m_dummyTracks [2] |

| PCB_ARC | m_dummyArcs [2] |

| PCB_VIA | m_dummyVias [2] |

| int | m_clearanceEpsilon |

| std::unordered_map< CLEARANCE_CACHE_KEY, int > | m_clearanceCache |

| std::unordered_map< CLEARANCE_CACHE_KEY, int > | m_tempClearanceCache |

| std::unordered_map< HULL_CACHE_KEY, SHAPE_LINE_CHAIN > | m_hullCache |

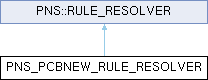

Detailed Description

Definition at line 159 of file pns_kicad_iface.cpp.

Constructor & Destructor Documentation

◆ PNS_PCBNEW_RULE_RESOLVER()

| PNS_PCBNEW_RULE_RESOLVER::PNS_PCBNEW_RULE_RESOLVER | ( | BOARD * | aBoard, |

| PNS::ROUTER_IFACE * | aRouterIface ) |

Definition at line 219 of file pns_kicad_iface.cpp.

References m_board, m_dummyTracks, and m_routerIface.

◆ ~PNS_PCBNEW_RULE_RESOLVER()

|

virtual |

Definition at line 243 of file pns_kicad_iface.cpp.

Member Function Documentation

◆ Clearance()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 747 of file pns_kicad_iface.cpp.

References PNS::CT_CLEARANCE, PNS::CT_EDGE_CLEARANCE, PNS::CT_HOLE_CLEARANCE, PNS::CT_HOLE_TO_HOLE, PNS::CT_PHYSICAL_CLEARANCE, PNS_LAYER_RANGE::End(), PNS_LAYER_RANGE::Intersection(), isCopper(), IsDrilledHole(), isEdge(), isHole(), IsNonPlatedSlot(), PNS::ITEM::Layers(), m_clearanceCache, m_clearanceEpsilon, m_tempClearanceCache, PNS::CONSTRAINT::m_Value, MINOPTMAX< T >::Min(), PNS::OWNABLE_ITEM::Owner(), PCB_LAYER_ID_COUNT, PCBNEW_LAYER_ID_START, QueryConstraint(), and PNS_LAYER_RANGE::Start().

◆ ClearanceEpsilon()

|

inlineoverridevirtual |

Reimplemented from PNS::RULE_RESOLVER.

Definition at line 193 of file pns_kicad_iface.cpp.

References m_clearanceEpsilon.

◆ ClearCacheForItems()

|

overridevirtual |

Reimplemented from PNS::RULE_RESOLVER.

Definition at line 689 of file pns_kicad_iface.cpp.

References m_clearanceCache, and m_hullCache.

◆ ClearCaches()

|

overridevirtual |

Reimplemented from PNS::RULE_RESOLVER.

Definition at line 714 of file pns_kicad_iface.cpp.

References m_clearanceCache, m_hullCache, and m_tempClearanceCache.

◆ ClearTemporaryCaches()

|

overridevirtual |

Reimplemented from PNS::RULE_RESOLVER.

Definition at line 722 of file pns_kicad_iface.cpp.

References m_tempClearanceCache.

◆ DpCoupledNet()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 1187 of file pns_kicad_iface.cpp.

References m_board.

◆ DpNetPair()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 1218 of file pns_kicad_iface.cpp.

References NETINFO_ITEM::GetNetname(), m_board, and PNS::ITEM::Net().

◆ DpNetPolarity()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 1205 of file pns_kicad_iface.cpp.

References m_board.

◆ getBoardItem()

|

private |

Definition at line 404 of file pns_kicad_iface.cpp.

References PNS::ITEM::Anchor(), PNS::ITEM::ARC_T, PNS::ITEM::HOLE_T, PNS::ITEM::Kind(), PNS::ITEM::LINE_T, m_dummyArcs, m_dummyTracks, m_dummyVias, PNS::ITEM::Net(), PNS::ITEM::SEGMENT_T, and PNS::ITEM::VIA_T.

Referenced by IsKeepout(), and QueryConstraint().

◆ HullCache()

|

overridevirtual |

Reimplemented from PNS::RULE_RESOLVER.

Definition at line 728 of file pns_kicad_iface.cpp.

References PNS::ITEM::Hull(), m_hullCache, and result.

◆ IsDrilledHole()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 363 of file pns_kicad_iface.cpp.

References BOARD_ITEM::HasDrilledHole(), isHole(), PNS::ITEM::Parent(), and PNS::ITEM::ParentPadVia().

Referenced by Clearance().

◆ IsInNetTie()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 248 of file pns_kicad_iface.cpp.

References PNS::ITEM::BoardItem(), BOARD_ITEM::GetParentFootprint(), and FOOTPRINT::IsNetTie().

◆ IsKeepout()

|

overridevirtual |

- Returns

- true if aObstacle is a keepout. Set aEnforce if said keepout's rules exclude aItem.

Implements PNS::RULE_RESOLVER.

Definition at line 287 of file pns_kicad_iface.cpp.

References getBoardItem(), ZONE::GetDoNotAllowFootprints(), ZONE::GetDoNotAllowPads(), ZONE::GetDoNotAllowTracks(), ZONE::GetDoNotAllowVias(), ZONE::GetIsRuleArea(), BOARD_ITEM::GetParentFootprint(), ZONE::HasKeepoutParametersSet(), PNS::ITEM::Layer(), m_routerIface, PNS::ITEM::Parent(), PCB_PAD_T, PCB_VIA_T, PCB_ZONE_T, and EDA_ITEM::Type().

◆ IsNetTieExclusion()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 256 of file pns_kicad_iface.cpp.

References PNS::ITEM::BoardItem(), BOARD_ITEM::GetParentFootprint(), FOOTPRINT::IsNetTie(), PNS::ITEM::Layer(), m_board, m_routerIface, PNS::ITEM::Net(), and NetCode().

◆ IsNonPlatedSlot()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 377 of file pns_kicad_iface.cpp.

References isHole(), NPTH, pad, PNS::ITEM::Parent(), PNS::ITEM::ParentPadVia(), PCB_PAD_T, and EDA_ITEM::Type().

Referenced by Clearance().

◆ NetCode()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 1193 of file pns_kicad_iface.cpp.

References m_routerIface.

Referenced by IsNetTieExclusion().

◆ NetName()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 1199 of file pns_kicad_iface.cpp.

References m_routerIface.

◆ QueryConstraint()

|

overridevirtual |

Implements PNS::RULE_RESOLVER.

Definition at line 436 of file pns_kicad_iface.cpp.

References PNS::ITEM::BoardItem(), chain, CLEARANCE_CONSTRAINT, PNS::LINE::CLine(), SHAPE_LINE_CHAIN::CPoint(), PNS::CT_CLEARANCE, PNS::CT_DIFF_PAIR_GAP, PNS::CT_DIFF_PAIR_SKEW, PNS::CT_EDGE_CLEARANCE, PNS::CT_HOLE_CLEARANCE, PNS::CT_HOLE_TO_HOLE, PNS::CT_LENGTH, PNS::CT_MAX_UNCOUPLED, PNS::CT_PHYSICAL_CLEARANCE, PNS::CT_VIA_DIAMETER, PNS::CT_VIA_HOLE, PNS::CT_WIDTH, DIFF_PAIR_GAP_CONSTRAINT, EDGE_CLEARANCE_CONSTRAINT, getBoardItem(), DRC_RULE::GetImplicitSource(), DRC_CONSTRAINT::GetName(), DRC_CONSTRAINT::GetOption(), DRC_CONSTRAINT::GetParentRule(), DRC_CONSTRAINT::GetSeverity(), DRC_CONSTRAINT::GetValue(), MINOPTMAX< T >::HasMin(), HOLE_CLEARANCE_CONSTRAINT, HOLE_SIZE_CONSTRAINT, HOLE_TO_HOLE_CONSTRAINT, BOX2< Vec >::Inflate(), BOX2< Vec >::Intersects(), DRC_RULE::IsImplicit(), DRC_CONSTRAINT::IsNull(), PNS::ITEM::Kind(), LENGTH_CONSTRAINT, PNS::ITEM::LINE_T, m_board, m_dummyTracks, PNS::CONSTRAINT::m_IsTimeDomain, m_routerIface, PNS::CONSTRAINT::m_RuleName, PNS::CONSTRAINT::m_Type, DRC_CONSTRAINT::m_Value, PNS::CONSTRAINT::m_Value, MAX_UNCOUPLED_CONSTRAINT, MINOPTMAX< T >::Min(), PNS::ITEM::Net(), BOX2< Vec >::Normalize(), PHYSICAL_CLEARANCE_CONSTRAINT, RPT_SEVERITY_IGNORE, SHAPE_LINE_CHAIN::SegmentCount(), BOX2< Vec >::SetEnd(), PCB_TRACK::SetEnd(), BOARD_CONNECTED_ITEM::SetLayer(), MINOPTMAX< T >::SetMin(), BOARD_CONNECTED_ITEM::SetNet(), BOX2< Vec >::SetOrigin(), PCB_TRACK::SetStart(), PCB_TRACK::SetWidth(), SKEW_CONSTRAINT, DRC_CONSTRAINT::TIME_DOMAIN, TRACK_WIDTH_CONSTRAINT, TUNING_PROFILE, and VIA_DIAMETER_CONSTRAINT.

Referenced by Clearance().

Member Data Documentation

◆ m_board

|

private |

Definition at line 207 of file pns_kicad_iface.cpp.

Referenced by DpCoupledNet(), DpNetPair(), DpNetPolarity(), IsNetTieExclusion(), PNS_PCBNEW_RULE_RESOLVER(), and QueryConstraint().

◆ m_clearanceCache

|

private |

Definition at line 213 of file pns_kicad_iface.cpp.

Referenced by Clearance(), ClearCacheForItems(), and ClearCaches().

◆ m_clearanceEpsilon

|

private |

Definition at line 211 of file pns_kicad_iface.cpp.

Referenced by Clearance(), and ClearanceEpsilon().

◆ m_dummyArcs

|

private |

Definition at line 209 of file pns_kicad_iface.cpp.

Referenced by getBoardItem().

◆ m_dummyTracks

|

private |

Definition at line 208 of file pns_kicad_iface.cpp.

Referenced by getBoardItem(), PNS_PCBNEW_RULE_RESOLVER(), and QueryConstraint().

◆ m_dummyVias

|

private |

Definition at line 210 of file pns_kicad_iface.cpp.

Referenced by getBoardItem().

◆ m_hullCache

|

private |

Definition at line 215 of file pns_kicad_iface.cpp.

Referenced by ClearCacheForItems(), ClearCaches(), and HullCache().

◆ m_routerIface

|

private |

Definition at line 206 of file pns_kicad_iface.cpp.

Referenced by IsKeepout(), IsNetTieExclusion(), NetCode(), NetName(), PNS_PCBNEW_RULE_RESOLVER(), and QueryConstraint().

◆ m_tempClearanceCache

|

private |

Definition at line 214 of file pns_kicad_iface.cpp.

Referenced by Clearance(), ClearCaches(), and ClearTemporaryCaches().

The documentation for this class was generated from the following file: