参考手册

| This manual is in the process of being revised to cover the latest stable release version of KiCad. It contains some sections that have not yet been completed. We ask for your patience while our volunteer technical writers work on this task, and we welcome new contributors who would like to help make KiCad’s documentation better than ever. |

版权

This document is Copyright © 2010-2022 by its contributors as listed below. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later.

本指南中的所有商标均属于其合法所有者。

贡献者

Jean-Pierre Charras, Fabrizio Tappero, Wayne Stambaugh, Graham Keeth

翻译人员

Liu HanCheng <[email protected]>, 2018.

taotieren <[email protected]>, 2019, 2020, 2021.

Telegram 简体中文交流群: https://t.me/KiCad_zh_CN

反馈

The KiCad project welcomes feedback, bug reports, and suggestions related to the software or its documentation. For more information on how to sumbit feedback or report an issue, please see the instructions at https://www.kicad.org/help/report-an-issue/

Introduction to the KiCad Schematic Editor

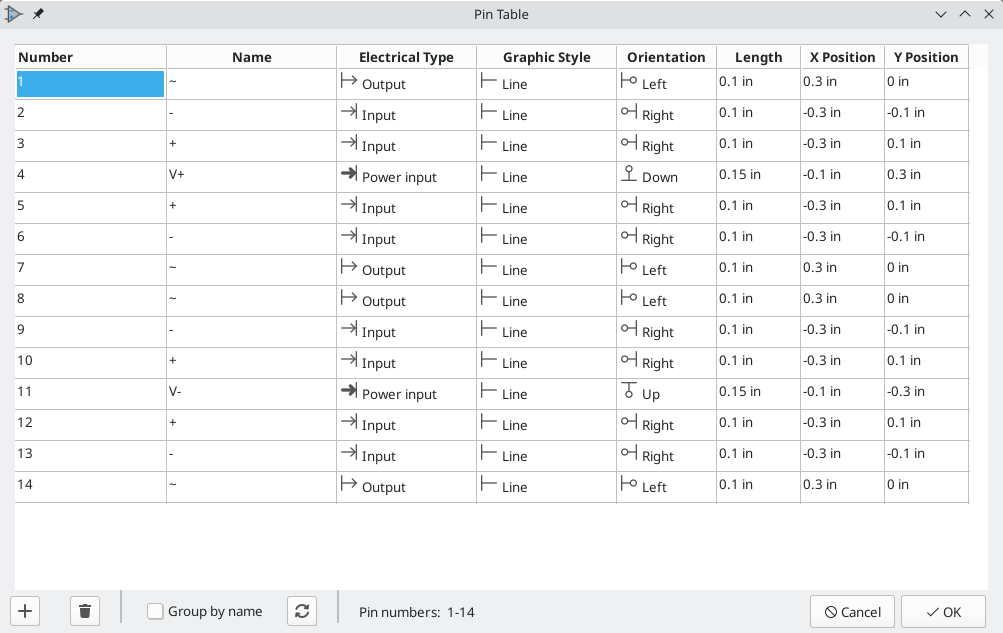

描述

The KiCad Schematic Editor is a schematic capture software distributed as a part of KiCad and available under the following operating systems:

-

Linux

-

Apple OS X

-

Windows

Regardless of the OS, all KiCad files are 100% compatible from one OS to another.

The Schematic Editor is an integrated application where all functions of drawing, control, layout, library management and access to the PCB design software are carried out within the editor itself.

The KiCad Schematic Editor is intended to cooperate with the KiCad PCB Editor, which is KiCad’s printed circuit design software. It can also export netlist files, which lists all the electrical connections, for other packages.

The Schematic Editor includes a symbol library editor, which can create and edit symbols and manage libraries. It also integrates the following additional but essential functions needed for modern schematic capture software:

-

电气规则检查(ERC),用于自动控制错误和缺失的连接

-

以多种格式导出绘图文件(Postscript,PDF,HPGL和SVG)

-

物料清单生成(通过 Python 或 XSLT 脚本,允许许多灵活的格式)。

The Schematic Editor supports multi-sheet schematics in several ways:

-

Flat hierarchies (schematic sheets are not explicitly connected in a master diagram).

-

Simple hierarchies (each schematic sheet is used only once).

-

Complex hierarchies (some schematic sheets are used multiple times).

Hierarchical schematics are described in detail later in the manual.

初始配置

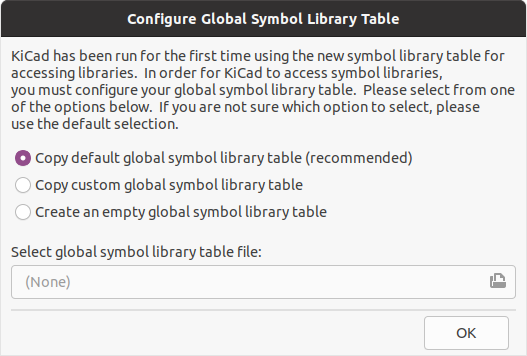

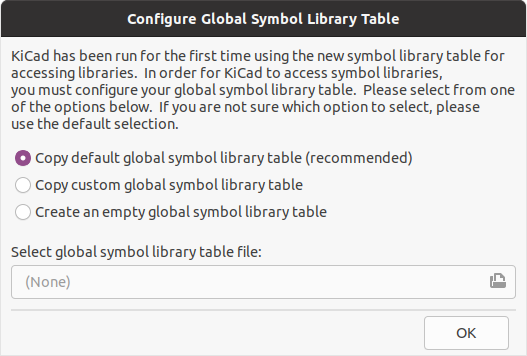

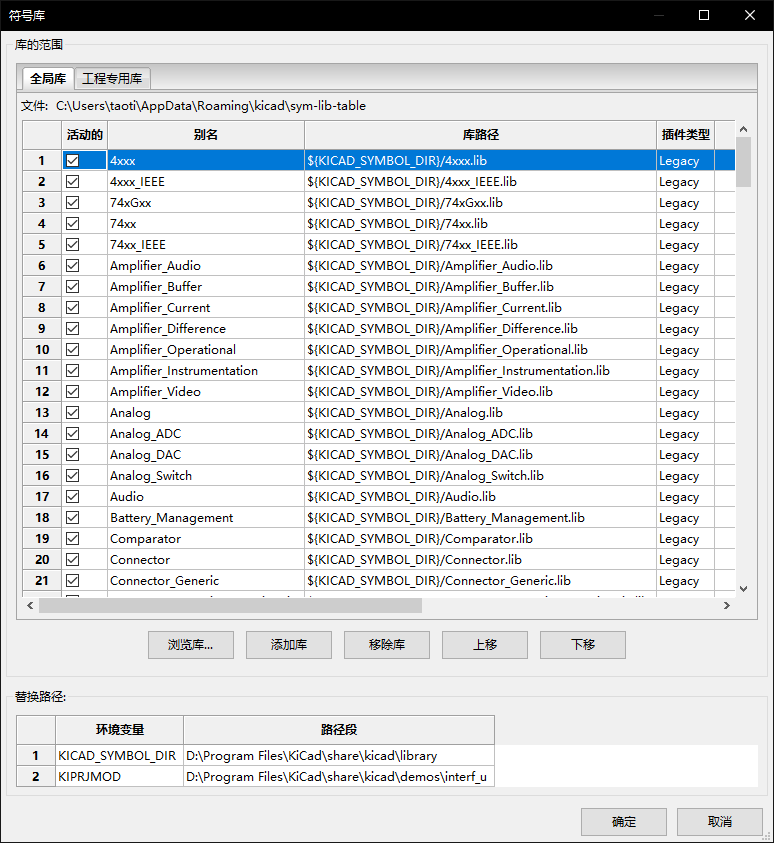

When the Schematic Editor is run for the first time, if the the global symbol library table file sym-lib-table is not found in the KiCad configuration folder then KiCad will ask how to create this file:

The first option is recommended (Copy default global symbol library table (recommended)). The default symbol library table includes all of the standard symbol libraries that are installed as part of KiCad.

If this option is disabled, KiCad was unable to find the default global symbol library table. This probably means you did not install the standard symbol libraries with KiCad, or they are not installed where KiCad expects to find them. On some systems the KiCad libraries are installed as a separate package.

-

If you have installed the standard KiCad symbol libraries and want to use them, but the first option is disabled, select the second option and browse to the

sym-lib-tablefile in the directory where the KiCad libraries were installed. -

If you already have a custom symbol library table that you would like to use, select the second option and browse to your

sym-lib-tablefile. -

If you want to construct a new symbol library table from scratch, select the third option.

Symbol library management is described in more detail later.

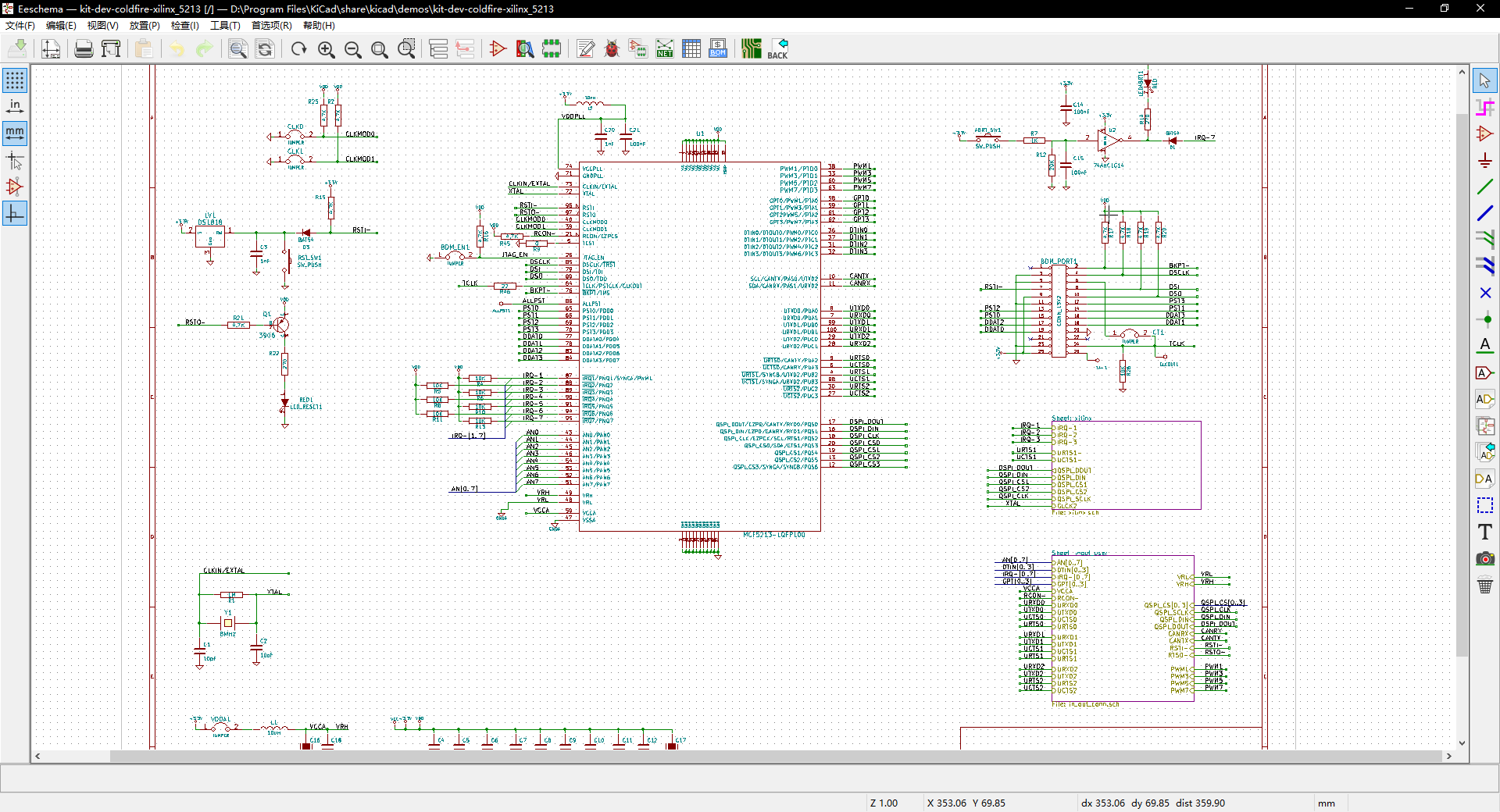

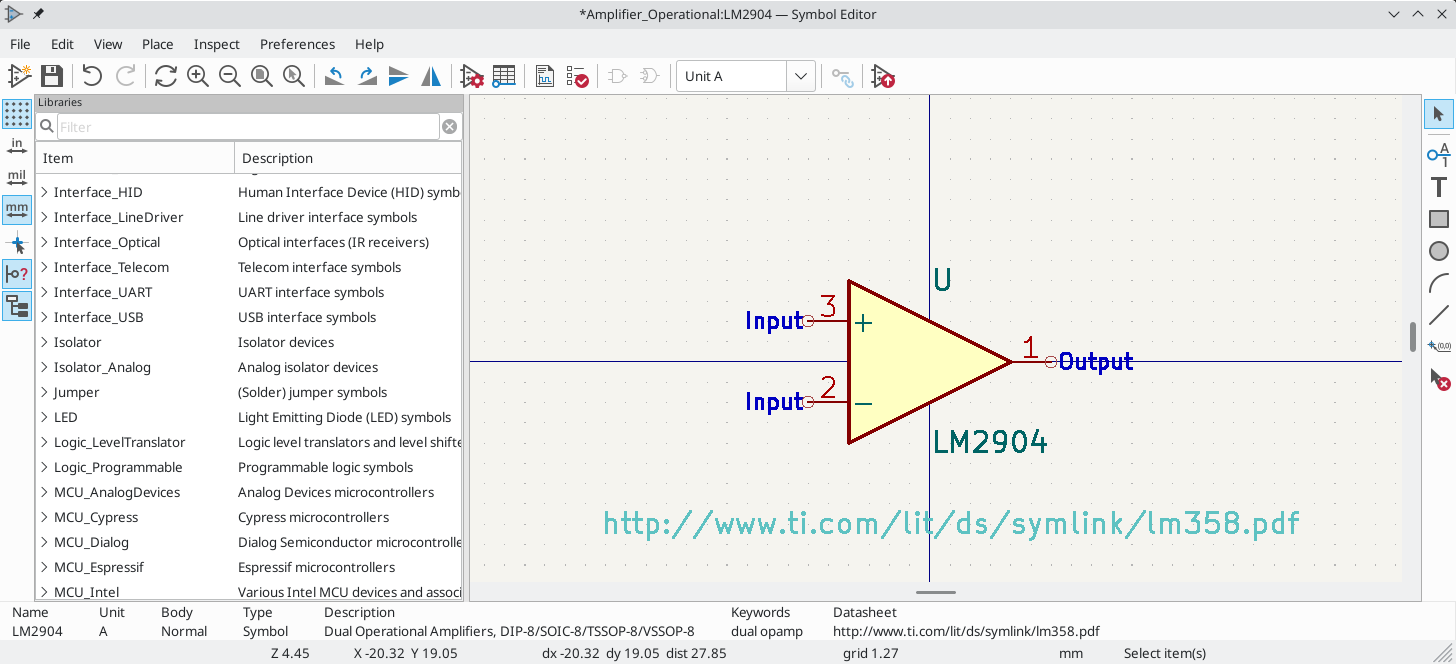

The Schematic Editor User Interface

The main Schematic Editor user interface is shown above. The center contains the main editing canvas, which is surrounded by:

-

Top toolbars (file management, zoom tools, editing tools)

-

Left toolbar (display options)

-

Message panel and status bar at bottom

-

Right panel (drawing and design tools)

Navigating the editing canvas

The editing canvas displays the schematic being designed. You can pan and zoom to different parts of the schematic and open any schematic sheet in the design.

By default, dragging with the middle or right mouse button will pan the canvas view and scrolling the mouse wheel will zoom the view in or out. You can change this behavior in the Mouse and Touchpad section of the preferences (see Configuration and Customization for details).

Several other zoom tools are available in the top toolbar:

-

zooms in on the center of the viewport.

zooms in on the center of the viewport. -

zooms out from the center of the viewport.

zooms out from the center of the viewport. -

zooms to fit the frame around the drawing sheet.

zooms to fit the frame around the drawing sheet. -

zooms to fit the items within the drawing sheet.

zooms to fit the items within the drawing sheet. -

allows you to draw a box to determine the zoomed area.

allows you to draw a box to determine the zoomed area.

The cursor’s current position is displayed at the bottom of the window (X and Y), along with the current zoom factor (Z), the cursor’s relative position (dx, dy, and dist), the grid setting, and the display units.

The relative coordinates can be reset to zero by pressing Space. This is useful for measuring distance between two points or aligning objects.

热键

The Ctrl+F1 shortcut displays the current hotkey list. The default hotkey list is included in the Actions Reference section of the manual.

The hotkeys described in this manual use the key labels that appear on a standard PC keyboard. On an Apple keyboard layout, use the Cmd key in place of Ctrl, and the Option key in place of Alt.

Many actions do not have hotkeys assigned by default, but hotkeys can be assigned or redefined using the hotkey editor (Preferences → Preferences… → Hotkeys).

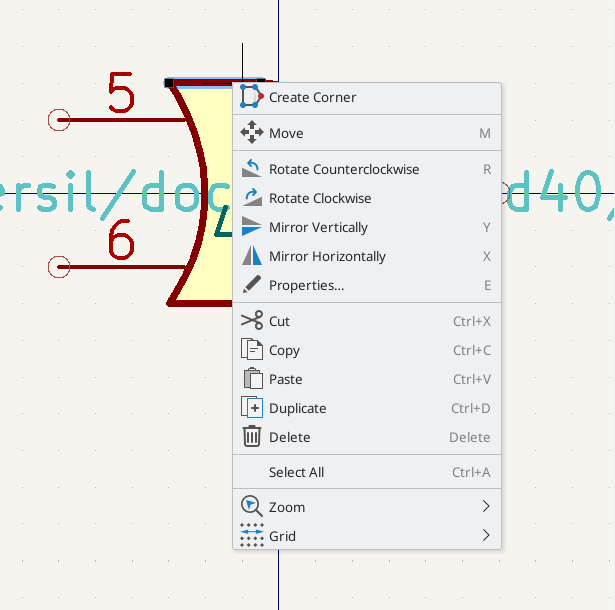

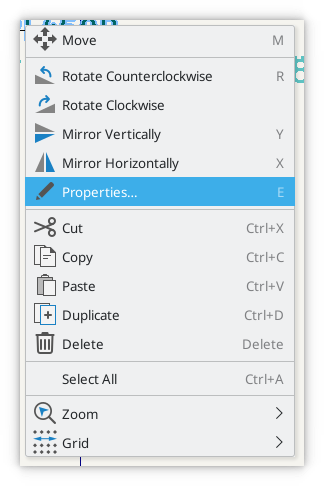

| Many of the actions available through hotkeys are also available in context menus. To access the context menu, right-click in the editing canvas. Different actions will be available depending on what is selected or what tool is active. |

Hotkeys are stored in the file user.hotkeys in KiCad’s configuration directory. The location is platform-specific:

-

Windows:

%APPDATA%\kicad\6.0\user.hotkeys -

Linux:

~/.config/kicad/6.0/user.hotkeys -

macOS:

~/Library/Preferences/kicad/6.0/user.hotkeys

KiCad can import hotkey settings from a user.hotkeys file using the Import Hotkeys button in the hotkey editor.

Mouse operations and selection

Selecting items in the editing canvas is done with the left mouse button. Single-clicking on an object will select it and dragging will perform a box selection. A box selection from left to right will only select items that are fully inside the box. A box selection from right to left will select any items that touch the box. A left-to-right selection box is drawn in yellow, with a cursor that indicates exclusive selection, and a right-to-left selection box is drawn in blue with a cursor that indicates inclusive selection.

The selection action can be modified by holding modifier keys while clicking or dragging. The following modifier keys apply when clicking to select single items:

| Modifier Keys (Windows) | Modifier Keys (Linux) | Modifier Keys (macOS) | Selection Effect |

|---|---|---|---|

Shift |

Shift |

Shift |

Add the item to the existing selection. |

Ctrl+Shift |

Ctrl+Shift |

Cmd+Shift |

Remove the item from the existing selection. |

long click |

long click or Alt |

long click or Option |

Clarify selection from a pop-up menu. |

Ctrl |

Ctrl |

Cmd |

Highlight the net of the selected copper item. |

The following modifier keys apply when dragging to perform a box selection:

| Modifier Keys (Windows) | Modifier Keys (Linux) | Modifier Keys (macOS) | Selection Effect |

|---|---|---|---|

Shift or Ctrl |

Shift or Ctrl |

Shift or Ctrl |

Add item(s) to the existing selection. |

Ctrl+Shift |

Ctrl+Shift |

Cmd+Shift |

Remove item(s) from the existing selection. |

Selecting an object displays information about the object in the message panel at the bottom of the window. Double-clicking an object opens a window to edit the object’s properties.

Pressing Esc will always cancel the current tool or operation and return to the selection tool. Pressing Esc while the selection tool is active will clear the current selection.

Left toolbar display controls

The left toolbar provides options to change the display of items in the Schematic Editor.

|

Turns grid display on/off. Note: by default, hiding the grid will disable grid snapping. This behavior can be changed in the Display Options section of Preferences. |

|

Display/entry of coordinates and dimensions in inches, mils, or millimeters. |

|

Switches between full-screen and small editing cursor (crosshairs). |

|

Turns invisible pin display on/off. |

|

Switches between free angle and horizontal/vertical placement of new wires, buses, and graphical lines. |

原理图创建和编辑

简介

A schematic designed with KiCad is more than a simple graphic representation of an electronic device. It is normally the entry point of a development chain that allows for:

-

验证一组规则(ERC,电气规则检查)以检测错误和遗漏。

-

Automatically generating a bill of materials.

-

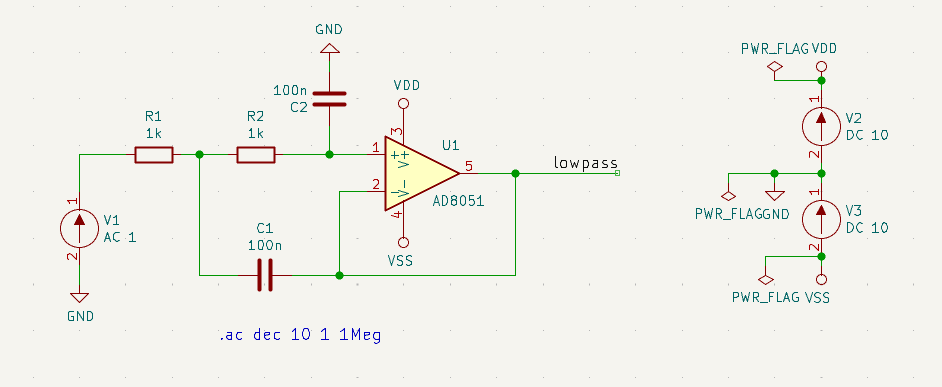

用于仿真软件(如 SPICE)的(创建 - 定制 - 网表和文件 - 文件,生成网表)。

-

Defining a circuit for transferring to PCB layout.

原理图主要由符号,电线,标签,连接点,总线和电源端口组成。 为了清晰起见,您可以放置纯粹的图形元素,如总线条目,注释和折线。

Symbols are added to the schematic from symbol libraries. After the schematic is made, the set of connections and footprints is imported into the PCB editor for designing a board.

Schematics can be contained in a single sheet or split among multiple sheets. In KiCad, multi-sheet schematics are organized hierarchically, with a root sheet and sub-sheet(s). Each sheet is its own .kicad_sch file and is itself a complete KiCad schematic. Working with hierarchical schematics is described in the Hierarchical Schematics chapter.

Schematic editing operations

Schematic editing tools are located in the right toolbar. When a tool is activated, it stays active until a different tool is selected or the tool is canceled with the Esc key. The selection tool is always activated when any other tool is canceled.

|

Selection tool (the default tool) |

|

Highlight a net by marking its wires and net labels with a different color. If the PCB Editor is also open then copper corresponding to the selected net will be highlighted as well. Net highlighting can be cleared by clicking with the highlight tool in an empty space, or by using the Clear Net Highlighting hotkey (~). |

|

Display the symbol selector dialog to place a new symbol. |

|

Display the power symbol selector dialog to place a new power symbol. |

|

Draw a wire. |

|

Draw a bus. |

|

Draw wire-to-bus entry points. These elements are only graphical and do not create a connection, thus they should not be used to connect wires together. |

|

Place a "No Connect" flag. These flags should be placed on symbol pins which are meant to be left unconnected. "No connect" flags indicate to the Electrical Rule Checker that the pin is intentionally unconnected and not an error. |

|

Place a junction. This connects two crossing wires or a wire and a pin, which can sometimes be ambiguous without a junction (i.e. if a wire end or a pin is not directly connected to another wire end). |

|

Place a local label. Local labels connect items located in the same sheet. For connections between two different sheets, use global or hierarchical labels. |

|

Place a global label. All global labels with the same name are connected, even when located on different sheets. |

|

Place a hierarchical label. Hierarchical labels are used to create a connection between a subsheet and the sheet’s parent sheet. See the Hierarchical Schematics section for more information about hierarchical labels, sheets, and pins. |

|

Place a hierarchical subsheet. You must specify the file name for this subsheet. |

|

Import a hierarchical pin from a subsheet. This command can be executed only on hierarchical subsheets. It will create hierarchical pins corresponding to hierarchical labels placed in the target subsheet. |

|

Draw lines. Note: Lines are graphical objects and are not the same as wires placed with the Wire tool. They do not connect anything. |

|

Place a text comment. |

|

Place a bitmap image. |

|

Delete clicked items. |

Grids

In the Schematic Editor the cursor always moves over a grid. The grid can be customized:

-

Size can be changed using the right click menu or using View → Grid Properties….

-

Color can be changed in the Colors page of the Preferences dialog (menu Preferences → General Options).

-

Visibility can be switched using the left-hand toolbar button.

The default grid size is 50 mil (0.050") or 1.27 millimeters.

This is the recommended grid for placing symbols and wires in a schematic, and for placing pins when designing a symbol in the Symbol Editor.

| Wires connect with other wires or pins only if their ends coincide exactly. Therefore it is very important to keep symbol pins and wires aligned to the grid. It is recommended to always use a 50 mil grid when placing symbols and drawing wires because the KiCad standard symbol library and all libraries that follow its style also use a 50 mil grid. Using a grid size other than 50 mil will result in schematics without proper connectivity! |

Smaller grids can also be used, but this is intended only for text and symbol graphics, and not recommended for placing pins and wires.

| Symbols, wires, and other elements that are not aligned to the grid can be snapped back to the grid by selecting them, right clicking, and clicking Align Elements to Grid. |

Snapping

Schematic elements such as symbols, wires, text, and graphic lines are snapped to the grid when moving, dragging, and drawing them. Additionally, the wire tool snaps to pins even when grid snapping is disabled. Both grid and pin snapping can be disabled while moving the mouse by using the modifier keys in the table below.

| On Apple keyboards, use the Cmd key instead of Ctrl. |

| Modifier Key | Effect |

|---|---|

Ctrl |

Disable grid snapping. |

Shift |

Disable snapping wires to pins. |

Working with symbols

Placing symbols

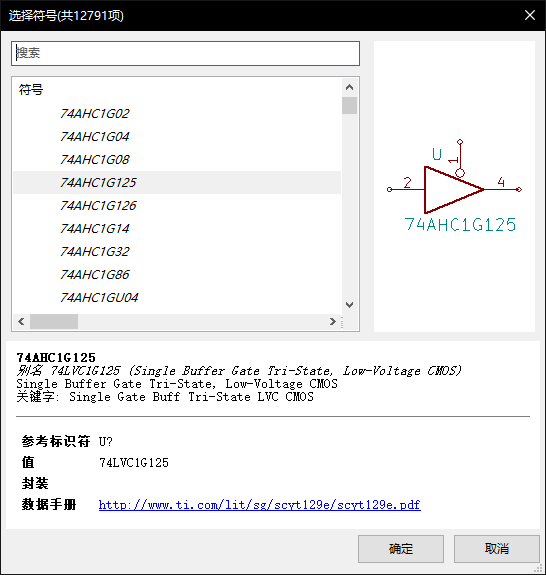

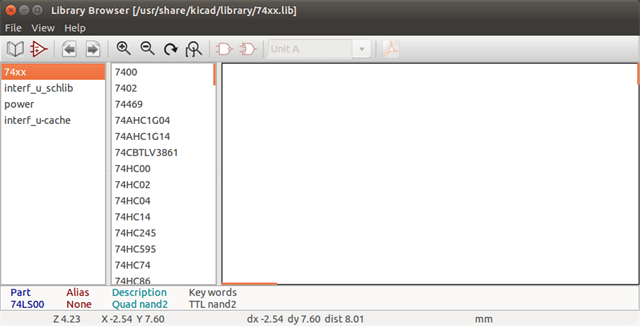

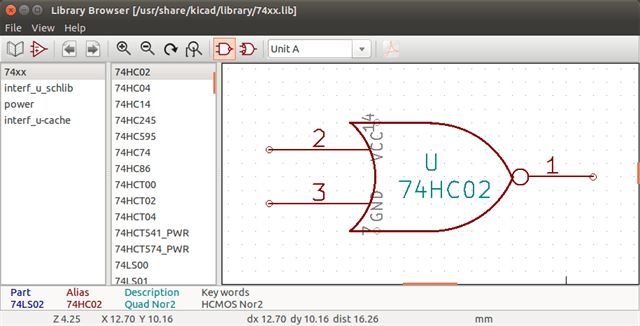

To load a symbol into your schematic you can use the icon ![]() . A dialog box allows you to type the name of the symbol to load.

. A dialog box allows you to type the name of the symbol to load.

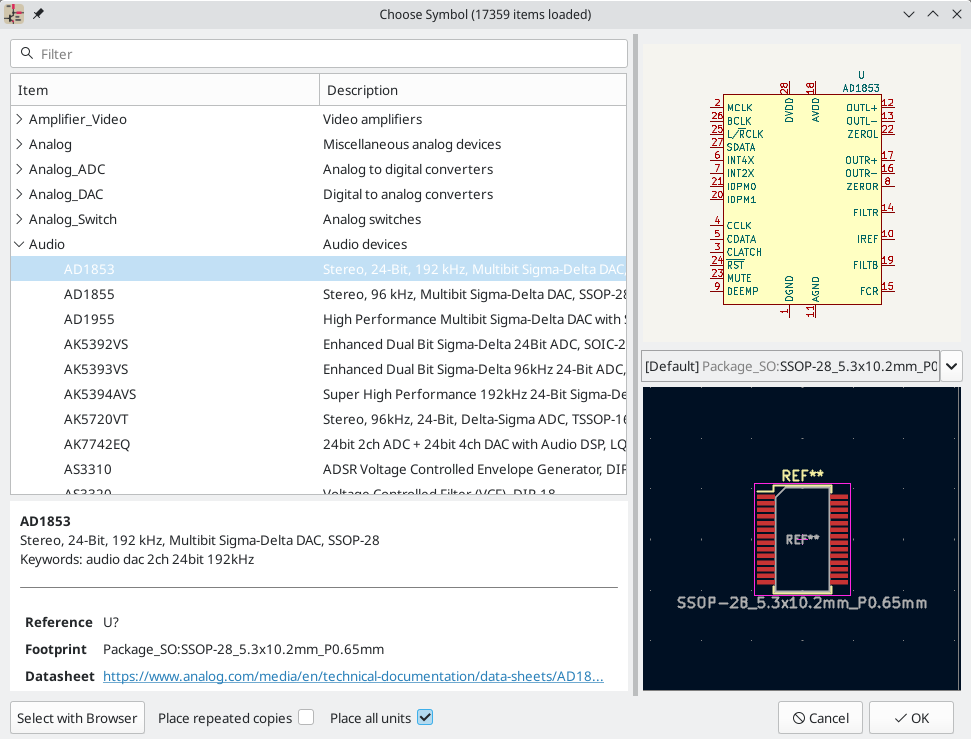

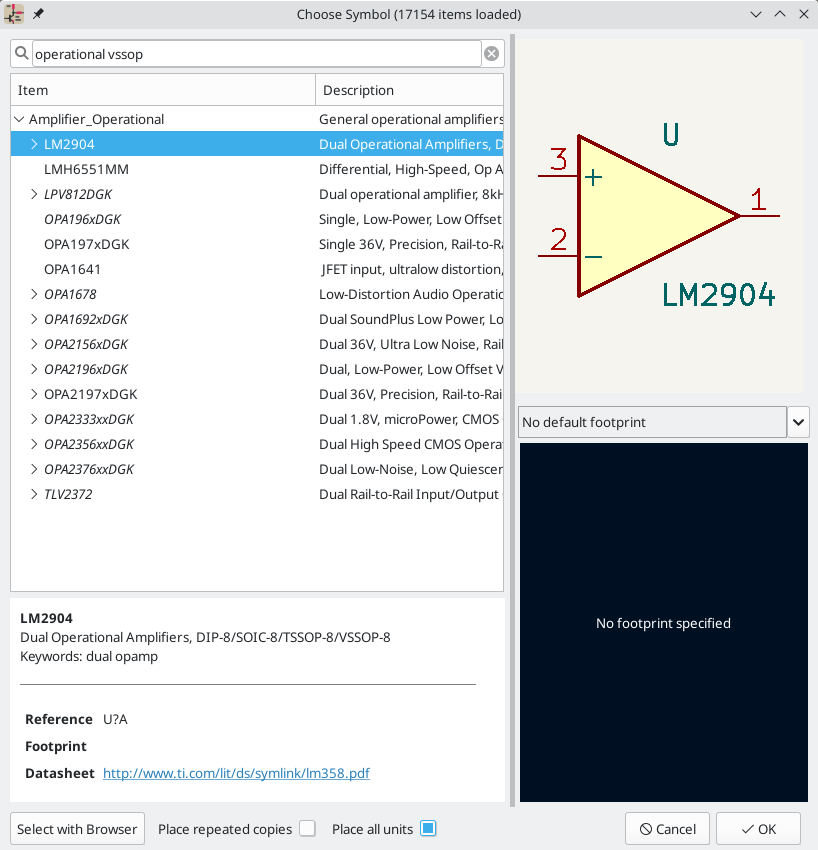

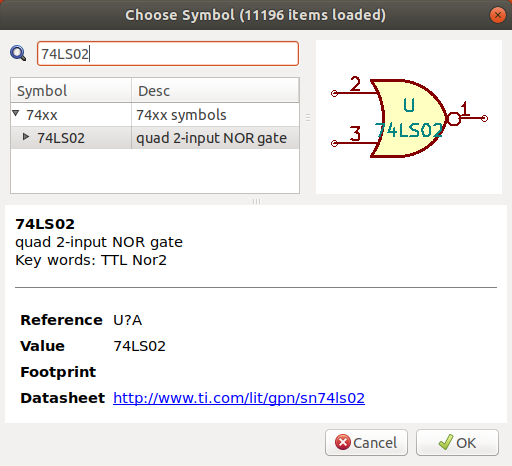

The Choose Symbols dialog will filter symbols by name, keywords, and description according to what you type into the search field.

Some advanced filters are available:

-

Wildcards: use the characters

?and*respectively to mean "any single character or no characters" and "any number of any characters, including none". -

Key-value pairs: if a library part’s description or keywords contain a tag of the format "Key:123", you can match relative to that by typing "Key>123" (greater than), "Key<123" (less than), etc. Numbers may include one of the following case-insensitive suffixes:

p

n

u

m

k

meg

g

t

10-12

10-9

10-6

10-3

103

106

109

1012

ki

mi

gi

ti

210

220

230

240

-

Regular expressions: if you’re familiar with regular expressions, these can be used too. The regular expression flavor used is the wxWidgets Advanced Regular Expression style, which is similar to Perl regular expressions.

If the symbol specifies a default footprint, this footprint will be previewed in the lower right. If the symbol includes footprint filters, alternate footprints that satisfy the footprint filters can be selected in the footprint dropdown menu at right.

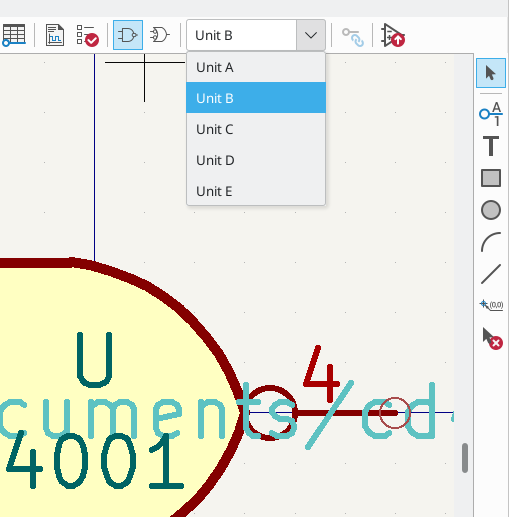

After selecting a symbol to place, the symbol will be attached to the cursor. Left clicking the desired location in the schematic places the symbol into the schematic. Before placing the symbol in the schematic, you can rotate it, mirror it, and edit its fields, by either using the hotkeys or the right-click context menu. These actions can also be performed after placement.

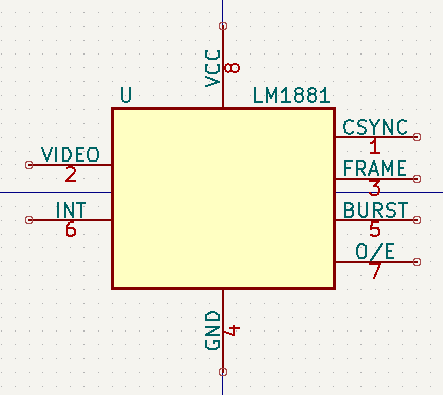

这是放置期间的符号:

If the Place repeated copies option is checked, after placing a symbol KiCad will start placing another copy of the symbol. This process continues until the user presses Esc.

For symbols with multiple units, if the Place all units option is checked, after placing the symbol KiCad will start placing the next unit in the symbol. This continues until the last unit has been placed or the user presses Esc.

Placing power ports

A power port symbol is a symbol representing a connection to a power net. The symbols are grouped in the power library, so they can be placed using the symbol chooser. However, as power placements are frequent, the ![]() tool is available. This tool is similar, except that the search is done directly in the

tool is available. This tool is similar, except that the search is done directly in the power library and any other library that contains power symbols.

Moving symbols

Symbols can be moved using the Move (M) or Drag (G) tools. These tools act on the selected symbol, or if no symbol is selected they act on the symbol under the cursor.

The Move tool moves the symbol itself without maintaining wired connections to the symbol pins.

The Drag tool moves the symbol without breaking wired connections to its pins, and therefore moves the connected wires as well.

You can also Drag symbols by clicking and dragging them with the mouse, depending on the Left button drag gesture setting in the Mouse and Touchpad section of Preferences.

Symbols can also be rotated (R) or mirrored in the X (X) or Y (Y) directions.

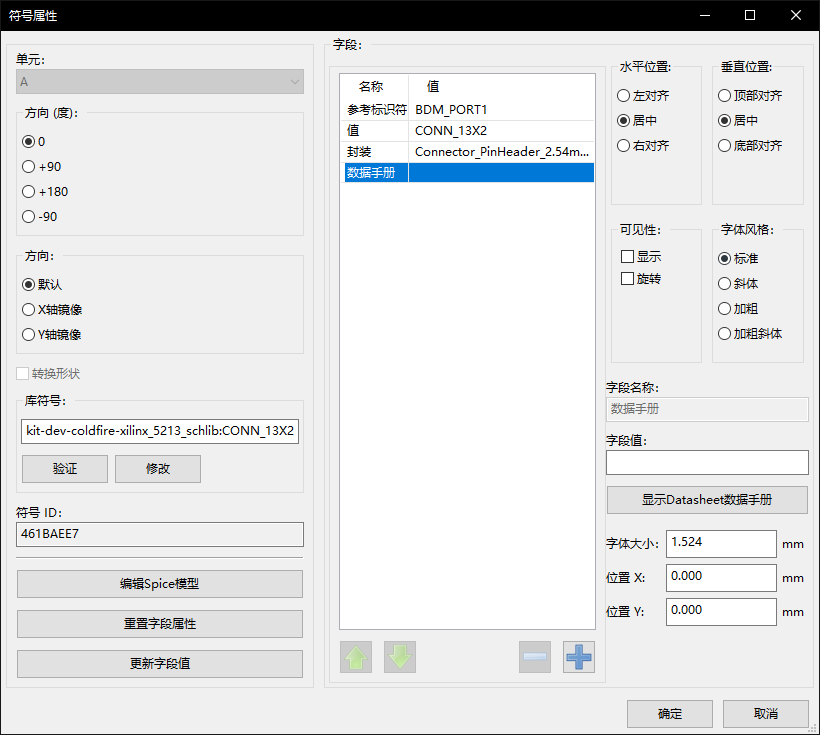

Editing symbol properties

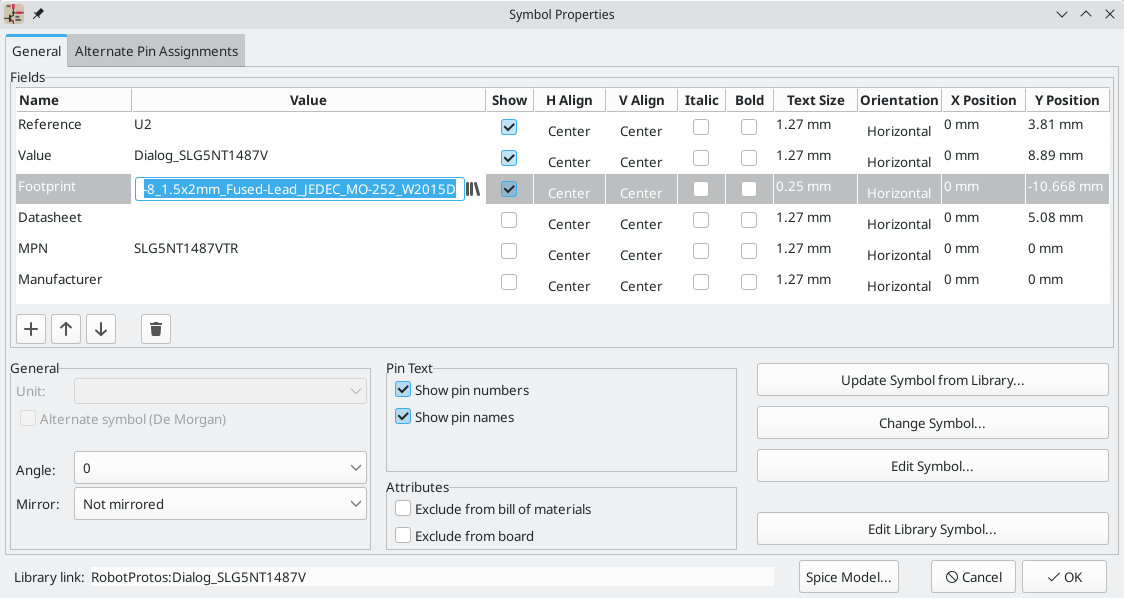

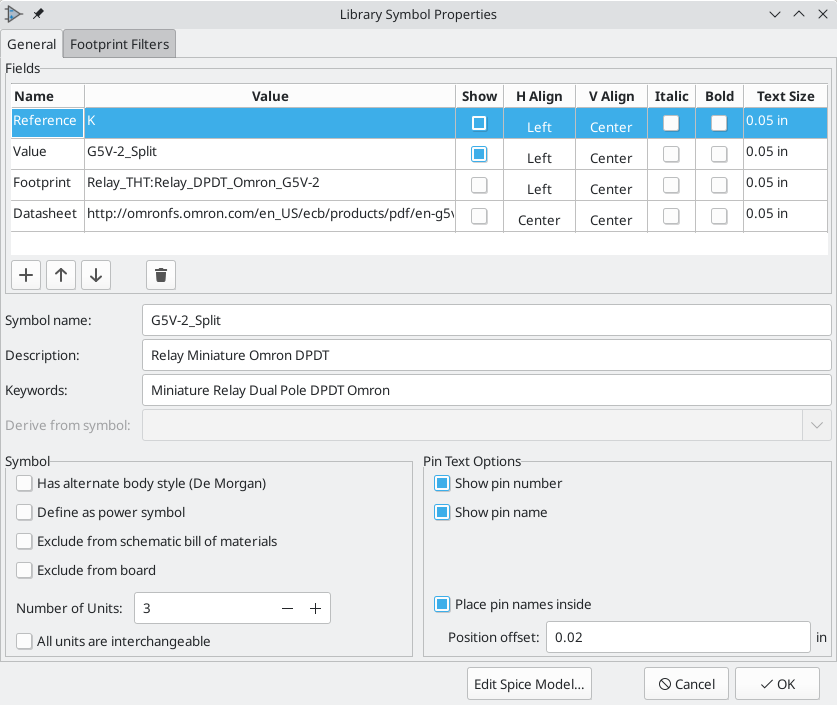

A symbol’s fields can be edited in the symbol’s Properties window. Open the Symbol Properties window for a symbol with the E hotkey or by double-clicking on the symbol.

The Symbol Properties window displays all the fields of a symbol in a table. New fields can be added, and existing fields can be deleted, edited, reordered, moved, or resized.

每个字段都可以是可见的或隐藏的,并且可以水平或垂直显示。 始终为正常显示的符号(无旋转或镜像)指示显示的位置,并且相对于符号的锚点。

The position and orientation properties of each field may be hidden in this dialog. They can be shown by right-clicking on the column header of the fields table and enabling the "Orientation", "X Position", and/or "Y Position" columns. Other columns can be shown or hidden as desired.

The "Update Symbol from Library…" button is used to update the schematic’s copy of the symbol to match the copy in the library. The "Change Symbol…" button is used to swap the current symbol to a different symbol in the library.

"Edit Symbol…" opens the Symbol Editor to edit the copy of the symbol in the schematic. Note that the original symbol in the library will not be modified. The "Edit Library Symbol…" button opens the Symbol Editor to edit the original symbol in the library. In this case, the symbol in the schematic will not be modified until the user clicks the "Update Symbol from Library…" button.

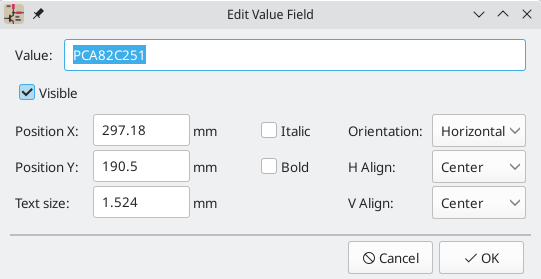

Editing symbol fields individually

An individual symbol text field can be edited directly with the E hotkey (with a field selected instead of a symbol) or by double-clicking on the field.

Some symbol fields have their own hotkey to edit them directly. With the symbol selected, the Reference, Value, and Footprint fields can be edited with the U, V, or F hotkeys, respectively.

The options in this dialog are the same as those in the full Symbol Properties dialog, but are specific to a single field.

Symbol fields can be automatically moved to an appropriate location with the Autoplace Fields action (select a symbol and press O). Field autoplacement is configurable in the Schematic Editor’s Editing Options, including a setting to always autoplace fields.

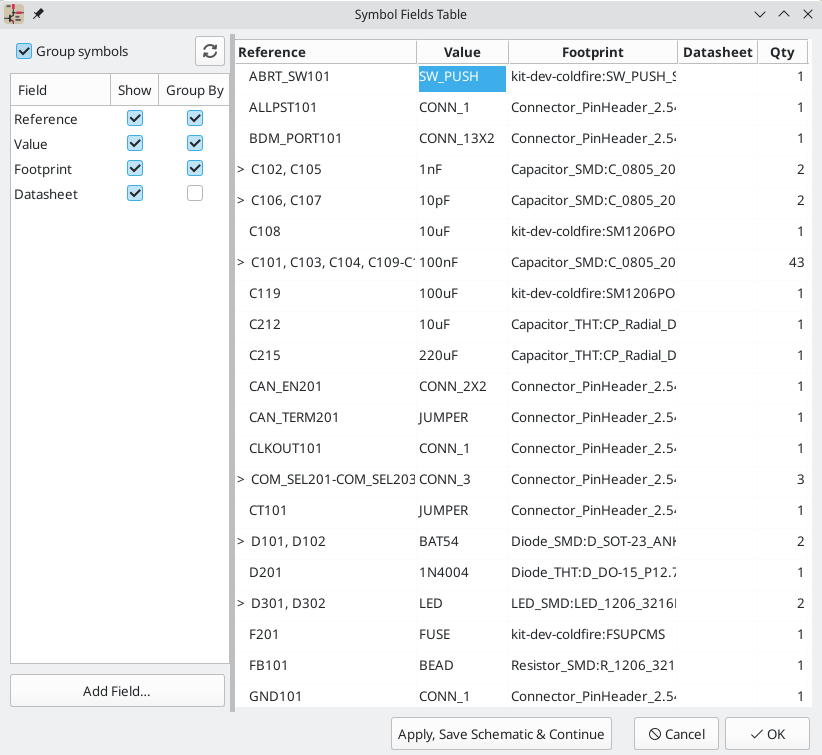

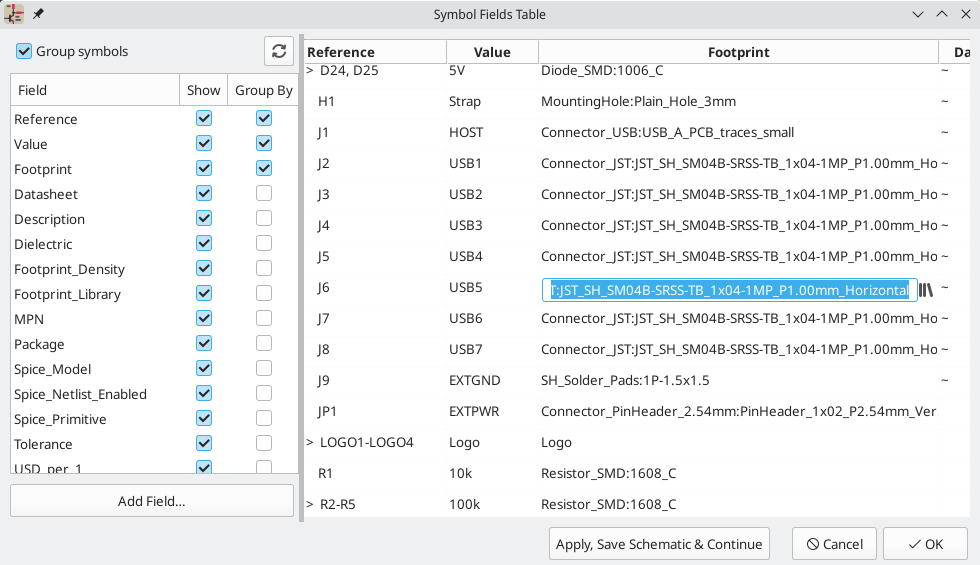

Symbol Fields Table

The Symbol Fields Table allows you to view and modify field values for all symbols in a spreadsheet interface. You can open the Symbol Fields Table with the ![]() button.

button.

Cells are navigated with the arrow keys, or with Tab / Shift+Tab to move right / left and Enter / Shift+Enter to move down / up, respectively.

A range of cells can be selected by clicking and dragging. The whole range of selected cells will be copied (Ctrl+C) or pasted into (Ctrl+V) on a copy or paste action. Copying a range of cells from the table can be useful for creating a BOM. More details of copying and pasting cells are described below.

Any symbol field can be shown or hidden using the Show checkboxes on the left, or by right-clicking on the header of the table. New symbol fields can be added using the Add Field… button.

Similar symbols can optionally be grouped by any symbol field using the Group By checkboxes. Grouped symbols are shown in a single row in the table. The grouped row can be expanded to show the individual symbols by clicking the arrow at the left of the row.

Tricks to simplify filling fields

There are several special copy/paste methods in the spreadsheet for pasting values into larger regions, including auto-incrementing pasted cells. These features may be useful when pasting values that are shared in several symbols.

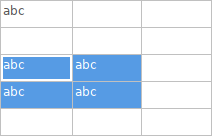

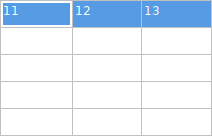

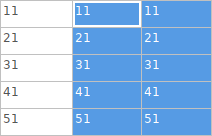

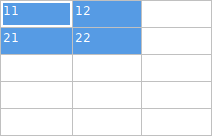

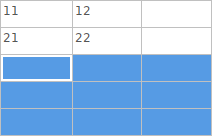

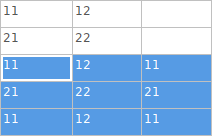

这些方法如下所示。

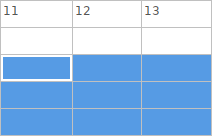

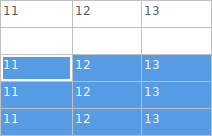

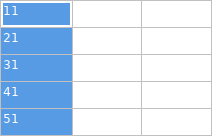

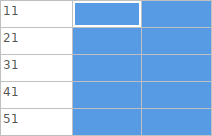

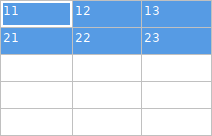

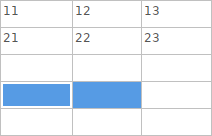

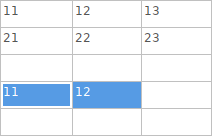

| 1. Copy (Ctrl+C) | 2. Select target cells | 3. Paste (Ctrl+V) |

|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 这些技术也可以在具有网格控制元素的其他对话框中使用。 |

Reference Designators and Symbol Annotation

Reference designators are unique identifiers for components in a design. They are often printed on a PCB and in assembly diagrams, and allow you to match symbols in a schematic to the corresponding components on a board.

In KiCad, reference designators consist of a letter indicating the type of component (R for resistor, C for capacitor, U for IC, etc.) followed by a number. If the symbol has multiple units then the reference designator will also have a trailing letter indicating the unit. Symbols that don’t have a reference designator set have a ? character instead of the number. Reference designators must be unique.

Reference designators can set manually by editing a symbol’s reference designator field, or automatically using the Annotation tool.

| The process of setting a symbol’s reference designator is called annotation. |

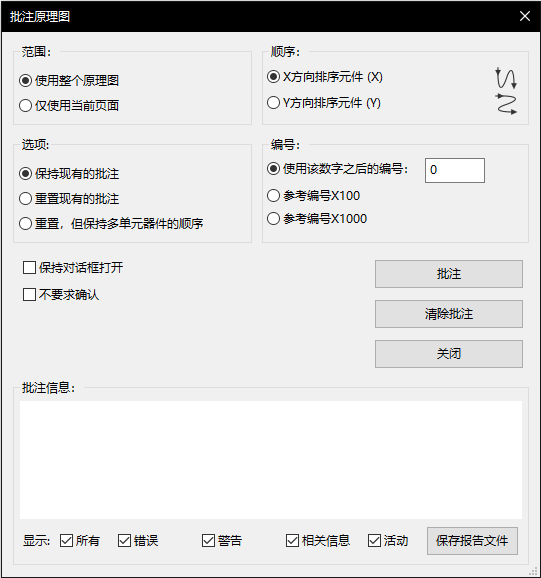

批注工具

The Annotation tool automatically assigns reference designators to symbols in the schematic. To launch the Annotation tool, click the ![]() button in the top toolbar.

button in the top toolbar.

The tool provides several options to control how symbols are annotated.

Scope: Selects whether annotation is applied to the entire schematic, to only the current sheet, or to only the selected symbols.

Options: Selects whether annotation should apply to all symbols and reset *existing reference designators, or apply only to unannotated symbols.

Order: Chooses the direction of numbering. If symbols are sorted by X position, all symbols on the left side of a schematic sheet will be lower numbered than symbols on the right side of the sheet. If symbols are sorted by Y position, all symbols on the top of a sheet will be lower numbered than symbols at the bottom of the sheet.

Numbering: Selects the starting point for numbering reference designators. The lowest unused number above the starting point is picked for each reference designator. The starting point can be an arbitrary number (typically zero), or it can be the sheet number multiplied by 100 or 1000 so that each part’s reference designator corresponds to the schematic page it is on.

The Clear Annotation button clears all reference designators in the selected scope.

Annotation messages can be filtered with the checkboxes at the bottom or saved to a report using the Save… button.

Electrical Connections

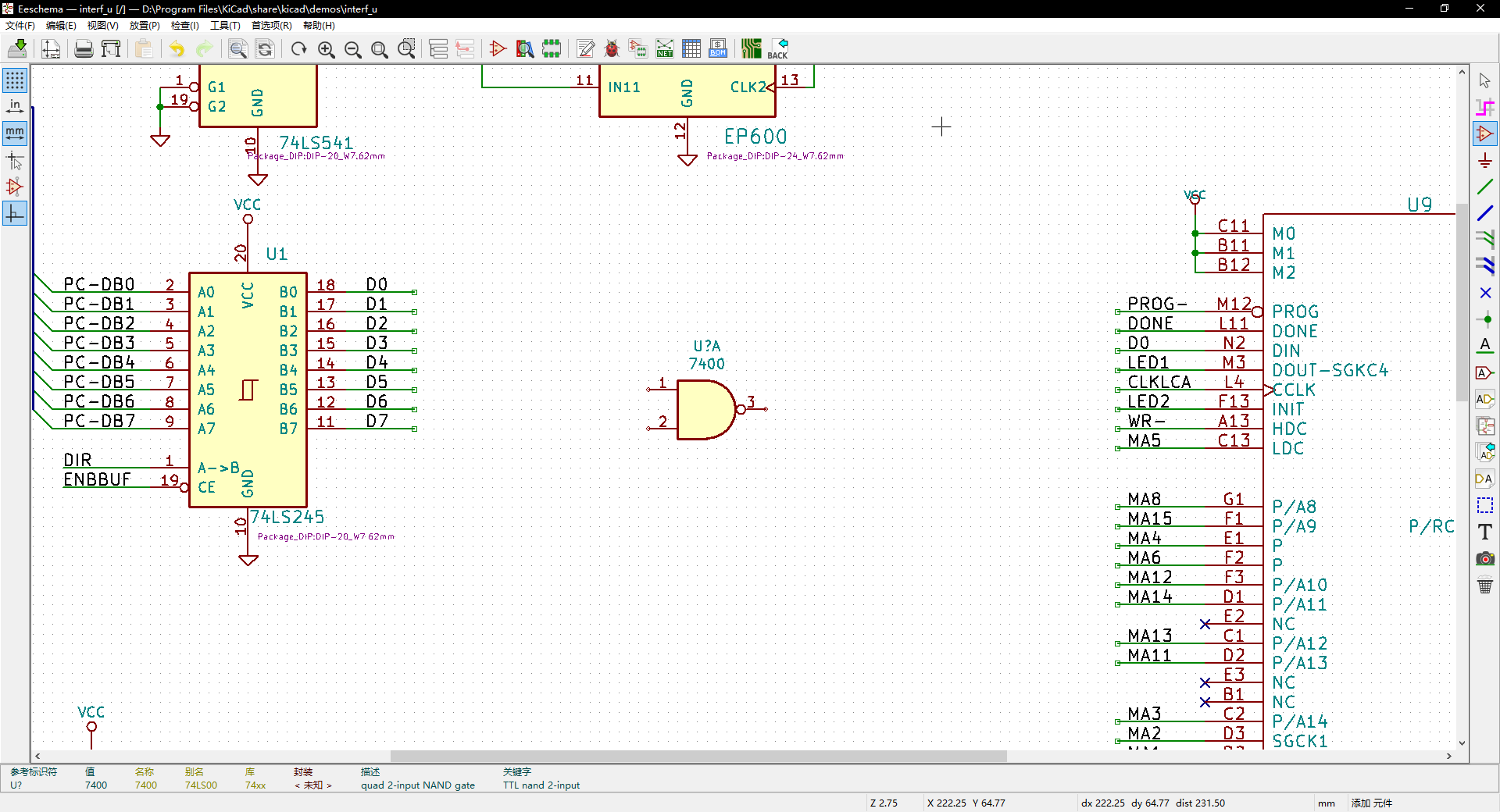

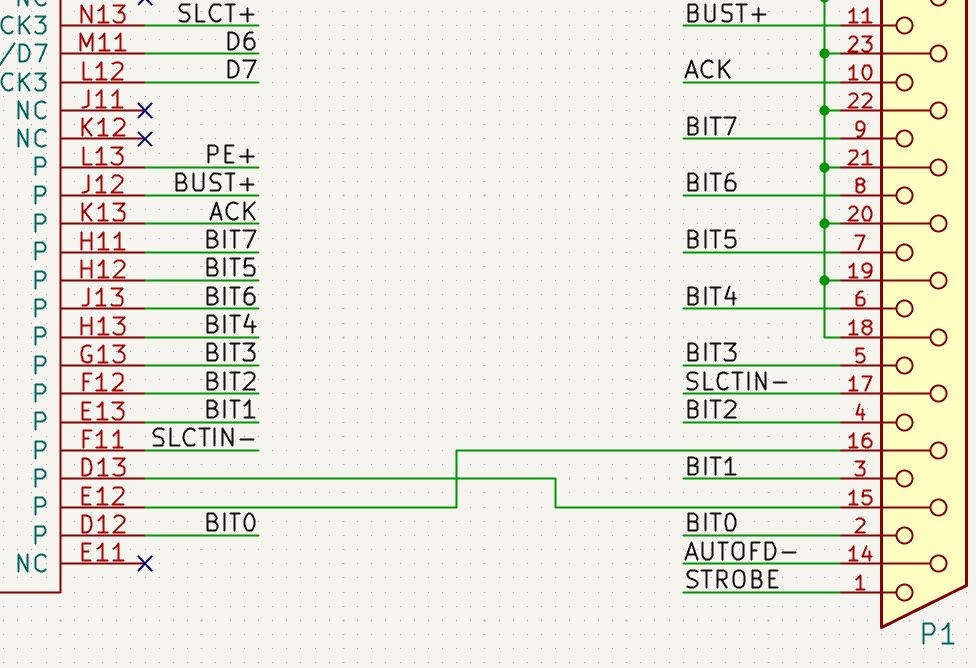

There are two primary ways to establish connections: wires and labels. Both are shown in the schematic below.

Connections can also be made with buses and with implicit connections via hidden power pins.

This section will also discuss two special types of symbols that can be added with the "Power port" button on the right toolbar:

-

Power ports: symbols for connecting wires to a power or ground net.

-

PWR_FLAG: a specific symbol for indicating that a net is powered when it is not connected to a power output pin (for example, a power net that is supplied by an off-board connector).

Label Connections

Labels are used to assign net names to wires and pins. Wires with the same net name are considered to be connected. A net can only have one name. If two different labels are placed on the same net, an ERC violation will be generated. Only one of the net names will be used in the netlist. The final net name is determined according to the rules described below.

There are three types of labels, each with a different connection scope.

-

Local labels, also referred to simply as labels, only make connections within a sheet. Add a local label with the

button in the right

toolbar.

button in the right

toolbar. -

Global labels make connections anywhere in a schematic, regardless of sheet. Add a global label with the

button in the right

toolbar.

button in the right

toolbar. -

Hierarchical labels connect to hierarchical sheet pins and are used in hierarchical schematics for connecting child sheets to their parent sheet. Add a hierarchical label with the

button in the right toolbar.

button in the right toolbar.

| Labels that have the same name will connect, regardless of the label type, if they are in the same sheet. |

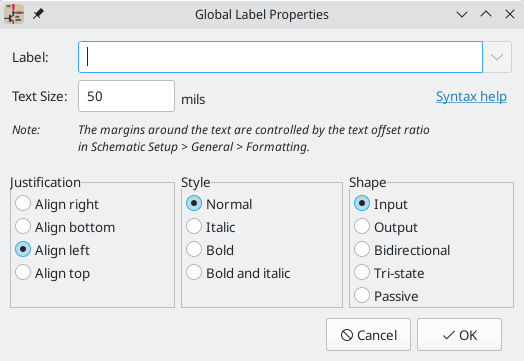

After using the appropriate button or hotkey to create a label, the Label Properties dialog appears.

The Label field sets the label’s text, which determines the net that the label assigns to its attached wire. Label text supports markup for overbars, subscripts, etc., as well as variable substitution. Use the Syntax help link in the dialog for a summary.

Justification sets the position of the label’s connection point relative to the label’s text. For example, when Align right is selected the connection point will be to the right of the text.

Text size and Style control the appearance of the label’s text. Shape controls the shape of the outline around the label; this is purely visual and has no electrical consequence. Local labels do not have an outline, and therefore do not have Shape options.

| Global labels have additional settings to control margins around the label text in the Schematic Setup dialog. |

After accepting the label properties, the label is attached to the cursor for placement. The connection point for a label is the small square in the corner of the label. The square disappears when the label is connected to a wire or the end of a pin.

The connection point’s position relative to the label text can be changed by choosing a different label orientation in the label’s properties, or by mirroring/rotating the label.

The Label Properties dialog can be accessed at any time by selecting a label and using the E hotkey, double-clicking on the label, or with Properties… in the right-click context menu.

Wire Connections

To establish a connection, a segment of wire must be connected by its end to another segment or to a pin. Only wire ends create connections; if a wire crosses the middle of another wire, a connection will not be made.

Unconnected wire ends have a small square that indicates the connection point. The square disappears when a connection is made to the wire end. Unconnected pins have a circle, which also disappears when a connection is made.

| Wires connect with other wires or pins only if their ends coincide exactly. Therefore it is important to keep symbol pins and wires aligned to the grid. It is recommended to always use a 50 mil grid when placing symbols and drawing wires because the KiCad standard symbol library and all libraries that follow its style also use a 50 mil grid. |

| Symbols, wires, and other elements that are not aligned to the grid can be snapped back to the grid by selecting them, right clicking, and selecting Align Elements to Grid. |

Drawing and editing wires

To begin connecting elements with wire, use the Wire tool ![]() in the right toolbar (w). Wires can also be automatically started by clicking on an unconnected symbol pin or wire end.

in the right toolbar (w). Wires can also be automatically started by clicking on an unconnected symbol pin or wire end.

Wires can be moved using the Move (M) or Drag (G) tools. As with symbols, the Move tool moves only the selected segment, without maintaining existing connections to other segments. The Drag tool maintains existing connections.

If a segment is selected or the cursor is over the middle of a wire, the move/drag action will move the entire segment. If the cursor is over a corner or wire end, the move/drag action will act on one end of the segment.

Wire Junctions

Wires that cross are not implicitly connected. It is necessary to join them by explicitly adding a junction dot if a connection is desired (![]() button in the right toolbar). Junction dots will be automatically added to wires that start or end on top of an existing wire.

button in the right toolbar). Junction dots will be automatically added to wires that start or end on top of an existing wire.

Junction dots are used in the schematic figure above on the wires connected to P1 pins 18, 19, 20, 21, 22, and 23.

Bus Connections

Buses are a way to group related signals in the schematic in order to simplify complicated designs. Buses can be drawn like wires using the bus tool ![]() , and are named using labels the same way signal wires are.

, and are named using labels the same way signal wires are.

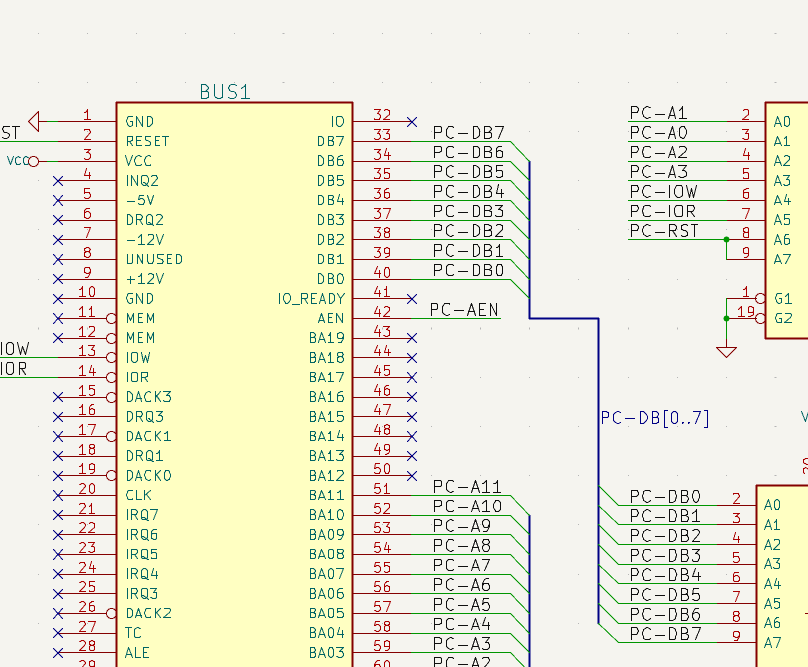

In the following schematic, many pins are connected to buses, which are the thick blue lines in the center.

总线编号

There are two types of bus in KiCad 6.0 and later: vector buses and group buses.

一个 向量总线 是以公共前缀开头并以数字结尾的信号集合。 向量总线命名为‘<PREFIX> [M..N]’,其中‘PREFIX’是任何有效的信号名称,‘M’是第一个后缀号,‘N’是最后一个后缀号。 例如,总线‘DATA [0..7]’包含信号‘DATA0’,‘DATA1’,依此类推,直到‘DATA7’。 指定‘M’和‘N’的顺序无关紧要,但两者都必须是非负的。

一个 组总线 是一个或多个信号和/或矢量总线的集合。 组总线可用于将相关信号捆绑在一起,即使它们具有不同的名称。 组总线使用特殊标签语法:

‘<OPTIONAL_NAME>{SIGNAL1 SIGNAL2 SIGNAL3}’

该组的成员列在由空格字符分隔的花括号(‘{}’)内。 该组的可选名称位于左大括号之前。 如果组总线未命名,则 PCB 上生成的网络将只是组内的信号名称。 如果组总线具有名称,则生成的网络将具有名称作为前缀,其中句点(‘.’)将前缀与信号名称分开。

例如,总线‘{SCL SDA}’有两个信号成员,在网表中这些信号将是‘SCL’和‘SDA’。 总线“USB1 {DP DM}”将生成名为“USB1.DP”和“USB1.DM”的网络。 对于在几个类似电路上重复使用较大总线的设计,使用这种技术可以节省时间。

组总线还可以包含矢量总线。 例如,总线‘MEMORY {A [7..0] D [7..0] OE WE}’包含矢量总线和普通信号,并将产生诸如“MEMORY.A7”和“MEMORY.OE”之类的网络在 PCB 上的 。

Bus wires can be drawn and connected in the same manner as signal wires, including using junctions to create connections between crossing wires. Like signals, buses cannot have more than one name — if two conflicting labels are attached to the same bus, an ERC violation will be generated.

总线成员之间的连接

Pins connected between the same members of a bus must be connected by labels. It is not possible to connect a pin directly to a bus; this type of connection will be ignored by KiCad.

在上面的示例中,连接是通过放置在连接到引脚的导线上的标签进行的。 到总线的总线入口(45度线段)仅是图形化的,并不是形成逻辑连接所必需的。

In fact, using the repetition command (Insert), connections can be very quickly made in the following way, if component pins are aligned in increasing order (a common case in practice on components such as memories, microprocessors…):

-

Place the first label (for example

PCA0) -

Use the repetition command as much as needed to place members. KiCad will automatically create the next labels (

PCA1,PCA2…) vertically aligned, theoretically on the position of the other pins. -

在第一个标签下画线。 然后使用重复命令将其他导线放在标签下。

-

如果需要,以相同的方式放置总线条目(放置第一个条目,然后使用重复命令)。

|

In the Schematic Editor → Editing Options section of the Preferences menu, you can set the repetition parameters:

|

总线正在展开

The unfold tool allows you to quickly break out signals from a bus. To unfold a signal, right-click on a bus object (a bus wire, etc) and choose Unfold from Bus. Alternatively, use the Unfold Bus hotkey (default: C) when the cursor is over a bus object. The menu allows you to select which bus member to unfold.

选择总线成员后,下一次单击将把总线成员标签放在所需位置。 该工具自动生成总线入口和导线,通向标签位置。 放置标签后,您可以继续放置其他线段(例如,连接到组件引脚)并以任何正常方式完成线缆。

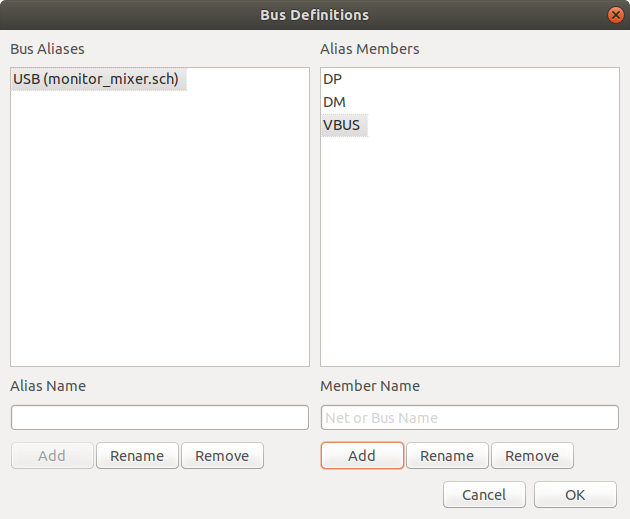

总线别名

总线别名是一种快捷方式,可让您更有效地使用大型组总线。 它们允许您定义组总线并为其指定一个简短的名称,然后可以在原理图中使用该名称而不是完整的组名。

To create bus aliases, open the Bus Definitions dialog in the Tools menu.

别名可以被命名为任何有效的信号名称。 使用该对话框,您可以向别名添加信号或矢量总线。 作为一种快捷方式,您可以键入或粘贴由空格分隔的信号和/或总线列表,并将它们全部添加到别名定义中。 在这个例子中,我们定义了一个名为‘USB’的别名,其成员为“DP”,“DM”和“VBUS”。

定义别名后,可以通过将别名放在组总线的大括号内来用于组总线标签:‘{USB}’。 这与标记总线“{DP DM VBUS}”具有相同的效果。 您还可以为组添加前缀名称,例如“USB1 {USB}”,这会产生如上所述的“USB1.DP”等网络。 对于复杂的总线,使用别名可以使原理图上的标签更短。 请记住,别名只是一个快捷方式,别名的名称不包含在网表中。

总线别名保存在原理图文件中。 在给定的原理图工作表中创建的任何别名都可用于同一层次结构设计中的任何其他原理图工作表。

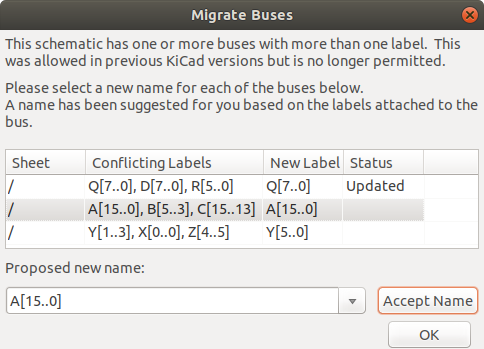

有多个标签的总线

KiCad 5.0 及更早版本允许将具有不同标签的总线连接在一起,并且在网络列表期间将加入这些总线的成员。 此行为已在 KiCad 6.0 中删除,因为它与组总线不兼容,并且还导致令人困惑的网表,因为不容易预测给定信号将接收的名称。

如果您在现代版本的 KiCad 中打开使用此功能的设计,您将看到“迁移总线”对话框,该对话框将指导您更新原理图,以便在任何给定的总线线路上只存在一个标签。

对于具有多个标签的每组总线,您必须选择要保留的标签。 下拉名称框允许您在设计中存在的标签之间进行选择,或者您可以通过手动将其输入新名称字段来选择其他名称。

Hidden Power Pins

When the power pins of a symbol are visible, they must be connected, as with any other signal. However, symbols such as gates and flip-flops are sometimes drawn with hidden power input pins which are connected implicitly.

KiCad automatically connects invisible pins with type "power input" to a global net with the same name as the pin. For example, if a symbol has a hidden power input pin named VCC, this pin will be globally connected to the VCC net on all sheets.

|

Hidden pins can be shown in the schematic by checking the Show hidden

pins option in the Schematic Editor → Display Options section

of the preferences, or by selecting View → Show hidden pins.

There is also a toggle icon |

It may be necessary to join power nets of different names (for example, GND in TTL components and VSS in MOS components). To accomplish this, add a power port symbol for each net and connect them with a wire.

If hidden power pins are used, it is not recommended to use local labels for power connection, as they will not connect to hidden power pins on other sheets.

| Care must be taken with hidden power input pins because they can create unintentional connections. By nature, hidden pins are invisible and do not display their pin name. This makes it easy to accidentally connect two power pins to the same net. For this reason, using invisible power pins in symbols is not recommended outside of power port symbols, and is only supported for compatibility with legacy designs and symbols. |

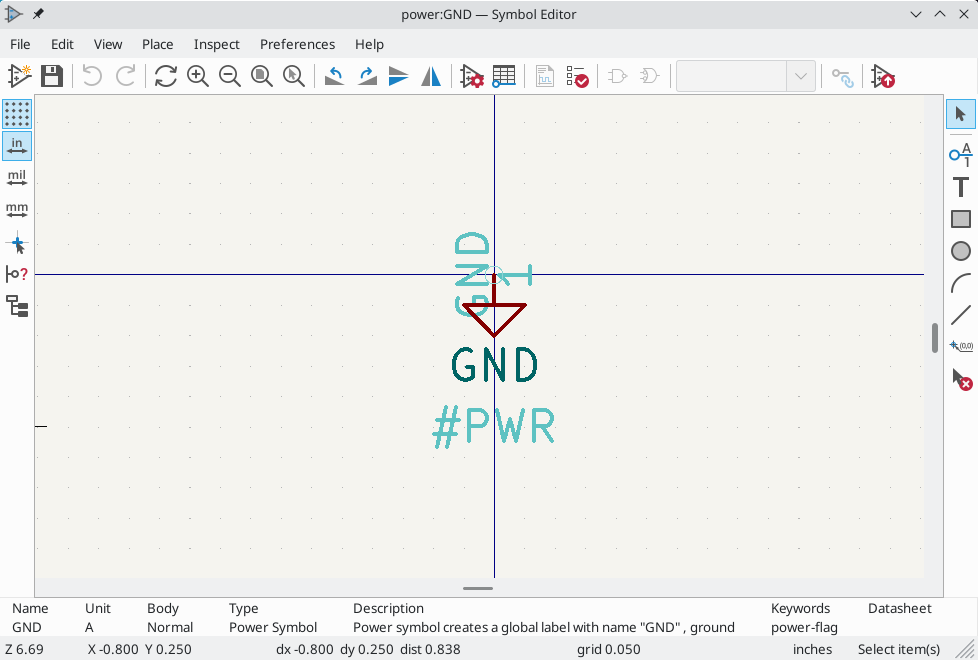

Power Ports

Power ports are symbols that are conventionally used to represent a connection to a power net, such as VCC or GND. In addition to being a visual indicator that the attached net is a power rail, power ports make global connections: two power ports with the same pin name connect to each other anywhere in the schematic, regardless of sheet.

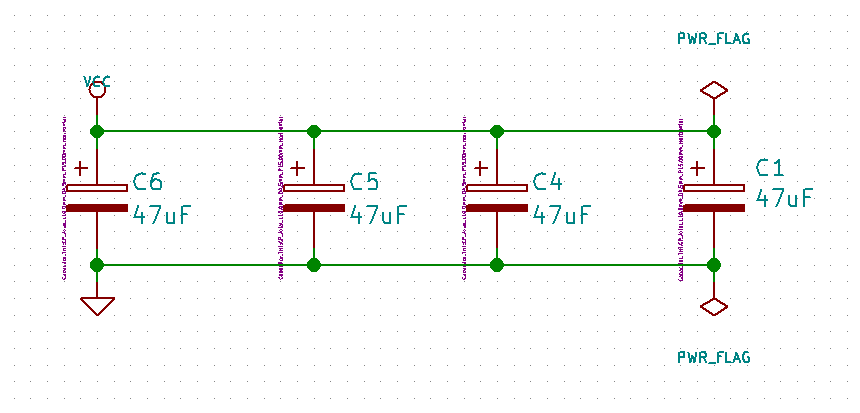

In the figure below, power port symbols are used to connect the positive and negative terminals of the capacitors to the VCC and GND nets, respectively.

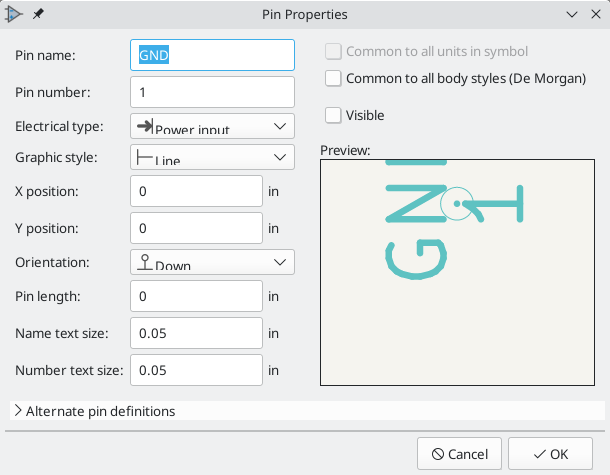

In the KiCad standard library, power ports are found in the power library, but power port symbols can be created in any library. To create a custom power port, make a new symbol with a power input pin that is set to be invisible. Name the pin according to the desired power net. In addition, set the "Define as power symbol" symbol property. As described in the hidden power pins section, invisible power input pins make global connections based on the hidden power pin’s name. The process of creating a power port is described in more detail in the Symbol Editor section.

| The connected net name is determined by the power port’s pin name, not the name or value of the symbol. This means that power port net names can only be changed in the symbol editor, not in the schematic. |

Net name assignment rules

Every net in the schematic is assigned a name, whether that name is specified by the user or automatically generated by KiCad.

When multiple labels are attached to the same net, the final net name is determined in the following order, from highest priority to lowest:

-

全局标签

-

Local labels

-

分层标签

-

Hierarchical sheet pins

If there are multiple labels of one type attached to a net, the names are sorted alphabetically and the first is used.

If a net travels through multiple sheets in a hierarchy, and has no global label or power port, it will take its name from the highest level of the hierarchy where it has a hierarchical label or local label. As described above, local labels take priority over hierarchical labels.

If none of the labels above are attached to a net, the net’s name is automatically generated based on the connected symbol pins.

PWR_FLAG

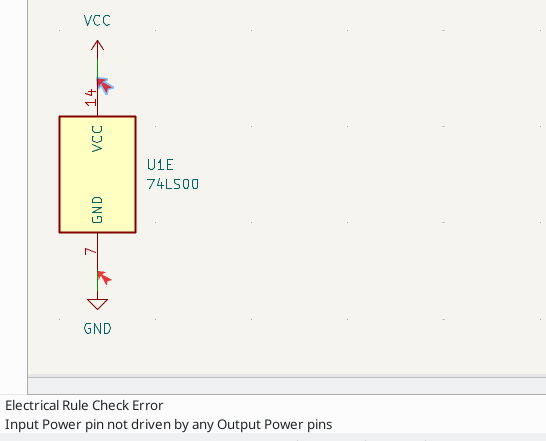

Two PWR_FLAG symbols are visible in the screenshot above. They indicate to ERC that the two power nets VCC and GND are actually connected to a power source, as there is no explicit power source such as a voltage regulator output attached to either net.

Without these two flags, the ERC tool would diagnose: Error: Input Power pin not driven by any Output Power pins.

The PWR_FLAG symbol is found in the power symbol library. The same effect can be achieved by connecting any power output pin to the net.

No-connection flag

No-connection flags (![]() ) are used to indicate that a pin is intentionally unconnected. These flags do not have any effect on the schematic’s connectivity, but they prevent "unconnected pin" ERC warnings for pins that are intentionally unconnected.

) are used to indicate that a pin is intentionally unconnected. These flags do not have any effect on the schematic’s connectivity, but they prevent "unconnected pin" ERC warnings for pins that are intentionally unconnected.

Graphical items

Text and graphic lines

It can be useful to place annotations such as text fields and frames to aid in understanding the schematic. Text fields (![]() ) and graphic lines (

) and graphic lines (![]() ) are intended for this use, as opposed to labels and wires, which are connection elements.

) are intended for this use, as opposed to labels and wires, which are connection elements.

The image below shows graphic lines and text in addition to wires, local labels, and hierarchical labels.

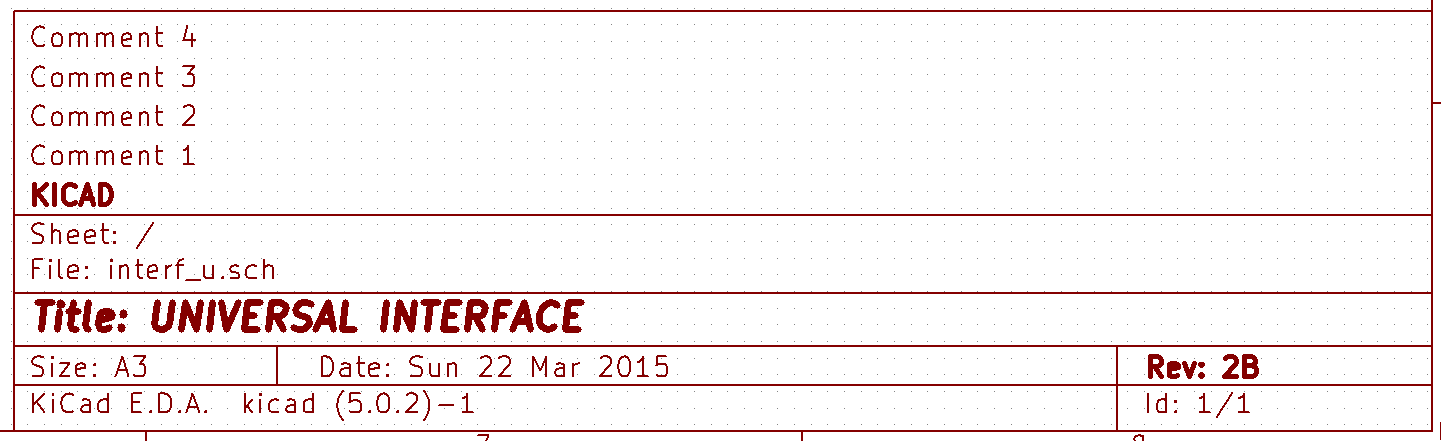

表格标题栏

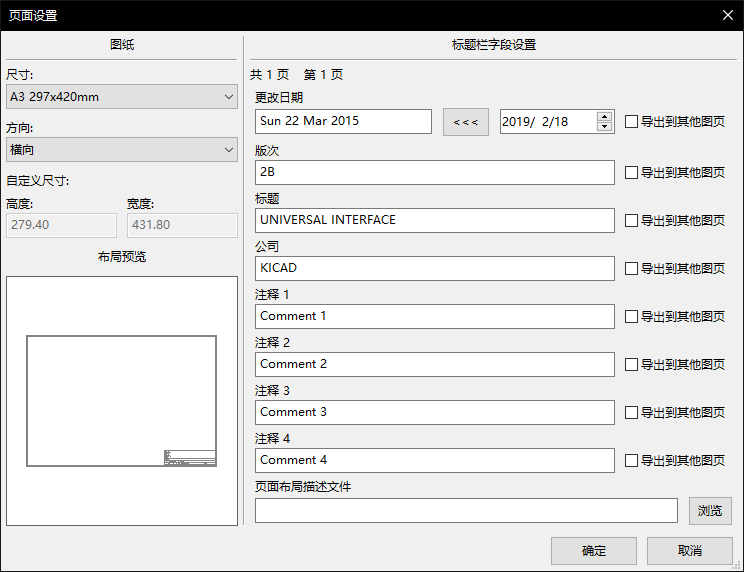

The title block is edited with the Page Settings tool (![]() ).

).

Each field in the title block can be edited, as well as the paper size and orientation. If the "Export to other sheets" option is checked for a field, that field will be updated in the title block of all sheets, rather than only the current sheet.

You can set the date to today’s or any other date by pressing the left arrow button by "Issue Date", but the date in the schematic will not be automatically updated.

A drawing sheet template file can also be selected.

The sheet number (Sheet X/Y) is automatically updated, but sheet page numbers can also be manually set using Edit → Edit Sheet Page Number….

Schematic Setup

The Schematic Setup window is used to set schematic options that are specific to the currently active schematic. For example, the Schematic Setup window contains formatting options, electrical rule configuration, netclass setup, and schematic text variable setup.

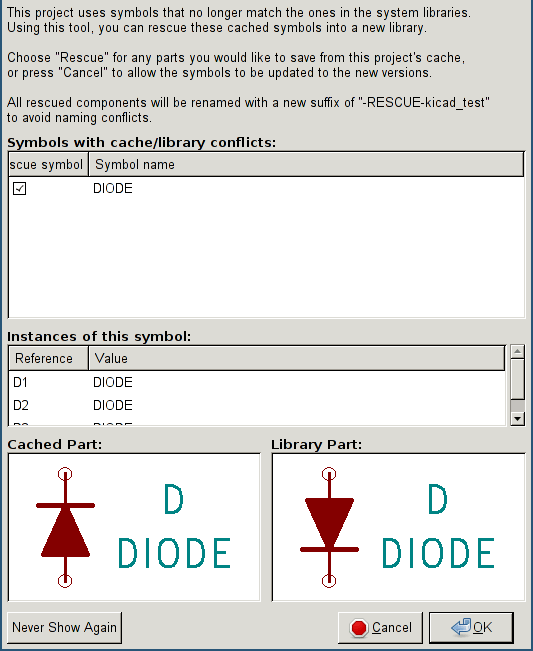

抢救缓存的符号

By default, KiCad loads symbols from the project libraries according to the set paths and library order. This can cause a problem when loading a very old project: if the symbols in the library have changed or have been removed or the library no longer exists since they were used in the project, the ones in the project would be automatically replaced with the new versions. The new versions might not line up correctly or might be oriented differently leading to a broken schematic.

When a project is saved, a cache library with the contents of the current library symbols is saved along with the schematic. This allows the project to be distributed without the full libraries. If you load a project where symbols are present both in its cache and in the system libraries, KiCad will scan the libraries for conflicts. Any conflicts found will be listed in the following dialog:

You can see in this example that the project originally used a diode with the cathode facing up, but the library now contains one with the cathode facing down. This change would break the schematic! Pressing OK here will cause the symbol cache library to be saved into a special rescue library and all the symbols are renamed to avoid naming conflicts.

If you press Cancel, no rescues will be made, so KiCad will load all the new components by default. If you save the schematic at this point, your cache will be overwritten and the old symbols will not be recoverable. If you have saved the schematic, you can still go back and run the rescue function again by selecting "Rescue Cached Components" in the "Tools" menu to call up the rescue dialog again.

如果您不想看到此对话框,可以按 从不再显示 。 默认设置是不执行任何操作并允许加载新元件。 可以在 库 首选项中更改此选项。

分层原理图

简介

In KiCad, multi-sheet schematics are hierarchical: there is a single root sheet, and additional sheets are created as subsheets of either the root sheet or another subsheet. Sheets can be included in a hierarchy multiple times, if desired.

Carefully drawing a schematic as a hierarchical design improves schematic legibility and reduces repetitive drawing.

Creating a hierarchical schematic starts from the root sheet. The process is to create a subsheet, then draw the circuit in the subsheet and make the necessary electrical connections between sheets. Connections can be made between nets in a subsheet and nets in the parent sheet using hierarchical pins and labels, or between any two nets in the hierarchy using global labels.

Adding sheets to a design

You can add a subsheet to a design with the Add Hierarchical Sheet tool (S hotkey, or the ![]() button in the right toolbar). Launch the tool, then click twice in the canvas to draw the upper left and lower right corners of the subsheet symbol. Make the sheet outline large enough to fit the hierarchical pins you will add later.

button in the right toolbar). Launch the tool, then click twice in the canvas to draw the upper left and lower right corners of the subsheet symbol. Make the sheet outline large enough to fit the hierarchical pins you will add later.

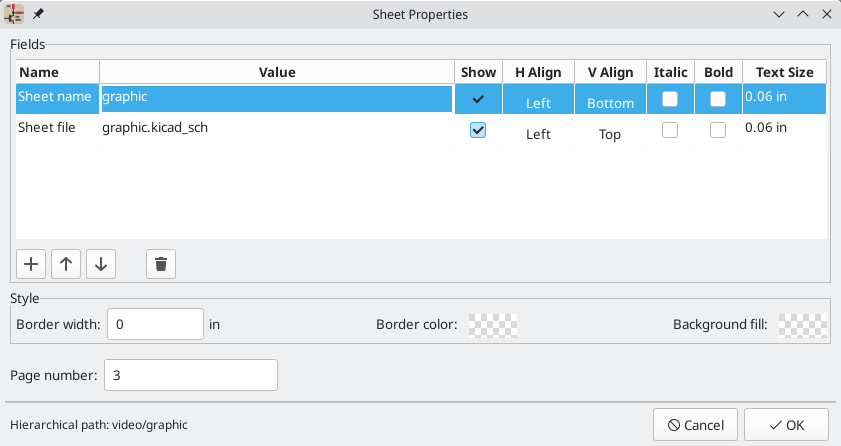

The Sheet Properties dialog will appear and prompt you for a sheet name and filename.

The sheet name must be unique, as it is used in the full net name for any nets in the subsheet. For example, a net with the local label net1 in the sheet sheet1 would have a full net name of /sheet1/net1. The sheet name is also used to refer to the sheet in various places in the GUI, including the title block and the hierarchy navigator.

The sheet filename specifies the file that the new sheet will be saved to or loaded from. The path to the sheet file can be relative or absolute. It is usually preferable to save subsheet files in the project directory and use a relative path so that the project is portable.

A single sheet file can be used more than once in a project by specifying the same filename for each repeated sheet; the circuit drawn in the sheet will be instantiated once per usage, and any edits in once instance will be reflected in the other instances.

| Sheet files can be shared between multiple projects to allow design reuse between projects. However, this is not recommended due to path portability concerns and the risk of unintentionally changing other projects while editing a shared sheet. |

The sheet’s page number is configurable here. The page number is displayed in the sheet title block and the hierarchy navigator, and sheets are sorted by page number in the hierarchy navigator and when printing or plotting.

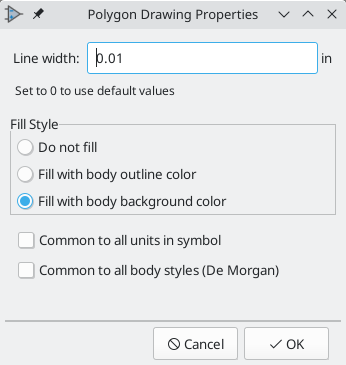

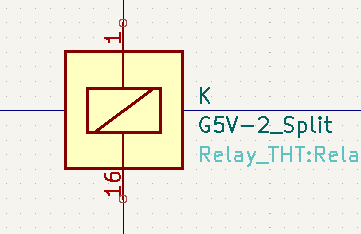

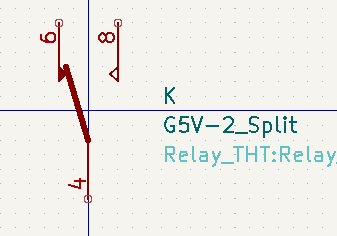

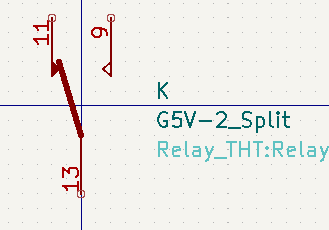

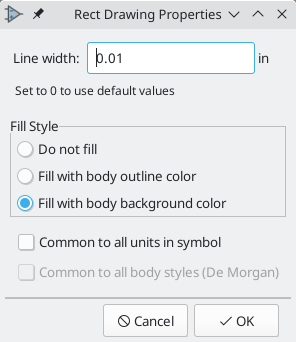

Several graphical options are also available. Border width sets the width of the border around the sheet shape. Border color and Background fill set the color for the border and fill of the sheet shape, respectively. If no color is set, a checkerboard swatch is shown and the default values from the color theme are used.

The Sheet Properties dialog can be accessed at any time by selecting a sheet symbol and using the E hotkey, or by right-clicking on a sheet symbol and selecting Properties….

Navigating between sheets

You can enter a hierarchical sheet from the parent sheet by double-clicking the child sheet’s shape, or right-clicking the child sheet and selecting Enter Sheet.

Return to the parent sheet by using the ![]() button in the top toolbar, or by right-clicking in an empty part of the schematic and clicking Leave Sheet.

button in the top toolbar, or by right-clicking in an empty part of the schematic and clicking Leave Sheet.

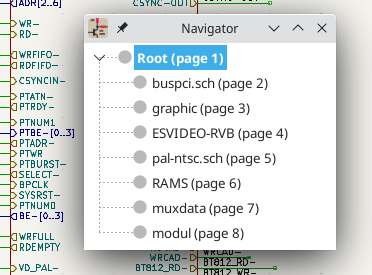

Alternatively, you can jump to any sheet with the hierarchy navigator. To open the hierarchy navigator, click the ![]() button in the top toolbar. Each sheet in the design is displayed as an item in the tree. Clicking a sheet name opens that sheet in the editing canvas.

button in the top toolbar. Each sheet in the design is displayed as an item in the tree. Clicking a sheet name opens that sheet in the editing canvas.

By default, the hierarchy navigator closes after a new sheet is opened. It can be configured to always remain open by selecting the Keep hierarchy navigator open option in the Editing Options section of the Schematic Editor preferences.

Electrical connections between sheets

Label overview

Electrical connections between sheets are made with labels. There are several kinds of labels in KiCad, each with a different connection scope.

-

Local labels only make connections within a sheet. Therefore local labels cannot be used to connect between sheets. Local labels are added with the

button.

button. -

Global labels make connections anywhere in a schematic, regardless of sheet. Global labels are added with the

button.

button. -

Hierarchical labels connect to hierarchical sheet pins accessible in the parent sheet. Hierarchical designs rely on hierarchical labels and pins to make connections between parent sheets and child sheets; you can think of hierarchical pins as defining the interface for a sheet. Hierarchical labels are added with the

button.

button.

| Labels that have the same name will connect, regardless of the label type, if they are in the same sheet. |

| Hidden power pins can also be considered global labels, because they connect anywhere in the schematic hierarchy. |

Hierarchical sheet pins

After placing hierarchical labels within the subsheet, matching hierarchical pins can be added to the subsheet symbol in the parent sheet. You can then make connections to the hierarchical pins with wires, labels, and buses. Hierarchical pins in a subsheet symbol are connected to the matching hierarchical labels in the subsheet itself.

| Hierarchical labels must be defined in the subsheet before the corresponding hierarchical sheet pin can be imported in the sheet symbol. |

For every hierarchical label in the subsheet, import the corresponding hierarchical pin into the sheet symbol by clicking the ![]() button in the right toolbar, then clicking on the sheet symbol. A sheet pin for the first unmatched hierarchical label will be attached to the cursor, where it can be placed anywhere along the border of the sheet symbol. Clicking again with the tool will continue to import additional sheet pins until there are no more hierarchical pins to import from the subsheet. Sheet pins can also be imported by selecting Import Sheet Pin in a sheet symbol’s right-click context menu.

button in the right toolbar, then clicking on the sheet symbol. A sheet pin for the first unmatched hierarchical label will be attached to the cursor, where it can be placed anywhere along the border of the sheet symbol. Clicking again with the tool will continue to import additional sheet pins until there are no more hierarchical pins to import from the subsheet. Sheet pins can also be imported by selecting Import Sheet Pin in a sheet symbol’s right-click context menu.

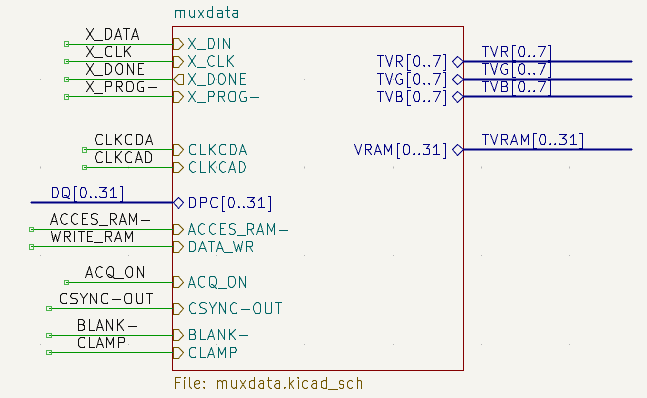

You can edit the properties of a sheet pin in the Sheet Pin Properties dialog. Open this dialog by double-clicking a sheet pin, selecting a sheet pin and using the E hotkey, or right-clicking a sheet pin and selecting Properties….

The sheet pin’s name can be edited in the textbox or by selecting from the dropdown list of hierarchical labels in the subsheet. A sheet pin’s name has to match the corresponding hierarchical label in the subsheet, so if a pin name is changed the label must change as well.

The connection type changes the shape of the sheet pin, and has no electrical effect. It can be set to Input, Output, Bidirectional, Tri-state, or Passive. The pin’s text size can also be changed.

Hierarchical design examples

Hierarchical designs can be put into one of several categories:

-

Simple: each sheet is used only once.

-

Complex: some sheets are instantiated multiple times.

-

Flat: a sub-case of a simple hierarchy, without connections between subsheets and their parent. Flat hierarchies can be used to represent a non-hierarchical design.

Each hierarchy model can be useful; the most appropriate one depends on the design.

Simple hierarchy

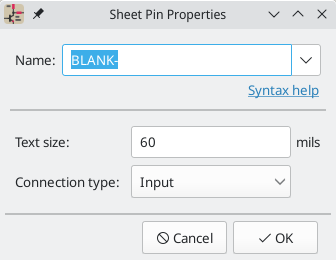

An example of a simple hierarchy is the video demo project included with KiCad. The root sheet contains seven unique subsheets, each with hierarchical labels and sheet pins linking the sheets to each other in the root sheet. Two of the subsheet symbols are shown below.

复杂层次结构

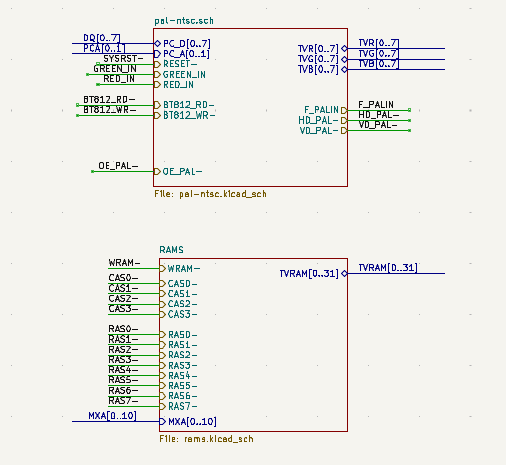

The complex_hierarchy demo project is an example of a complex hierarchy. The root sheet contains two subsheet symbols, which both refer to the same sheet file (ampli_ht.kicad_sch). This allows the design to include two copies of the same amplifier circuit. Although the two sheet symbols refer to the same filename, the sheet names are unique (ampli_ht_vertical and ampli_ht_horizontal). Inside each subsheet the circuits are identical except for the reference designators, which as always are unique.

This project contains no sheet pin connections. The only connections between the root sheet and the subsheets are global power connections made with power port symbols. However, sheets in a complex hierarchy could include sheet pin connections if appropriate for the design.

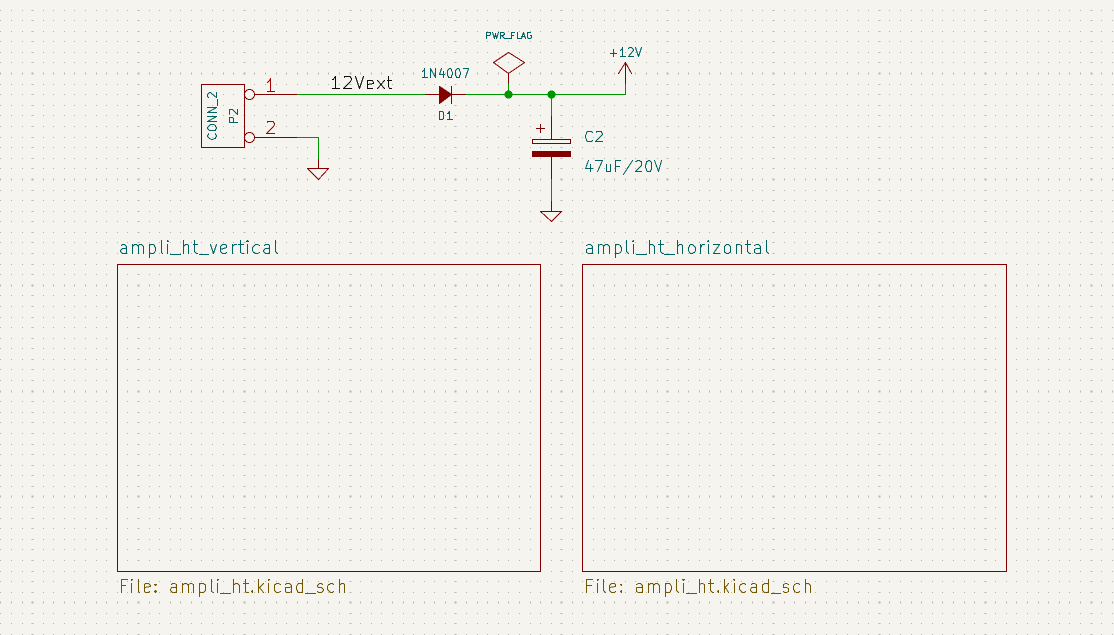

平面层次结构

The flat_hierarchy demo project is an example of a flat hierarchy. The root sheet contains two unique subsheet symbols with no hierarchical sheet pins. The root sheet in this project does nothing except hold the subsheets, and the subsheets are used only as additional pages in the schematic.

| This is the simplest way to create multi-page schematics in KiCad. |

Inspecting a schematic

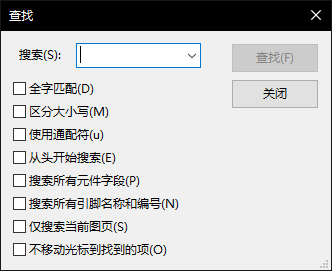

Find tool

The Find tool searches for text in the schematic, including reference designators, pin names, symbol fields, and graphic text. When the tool finds a match, the canvas is zoomed and centered on the match and the text is highlighted. Launch the tool using the ![]() button in the top toolbar.

button in the top toolbar.

The Find tool has several options:

Match case: Selects whether the search is case-sensitive.

Words: When selected, the search will only match the search term with complete words in the schematic. When unselected, the search will match if the search term is part of a larger word in the schematic.

Wildcards: When selected, wildcards can be used in the search terms. ?

matches any single character, and * matches any number of characters. Note

that when this option is selected, partial matches are not returned: searching

for abc* will match the string abcd, but searching for abc will not.

Search pin names and numbers: Selects whether the search should apply to pin names and numbers.

Search hidden fields: Selects whether the search should apply only to visible fields or if it should include hidden symbol fields.

Search the current sheet only: Selects whether the search should be limited to the current schematic sheet or to the entire schematic.

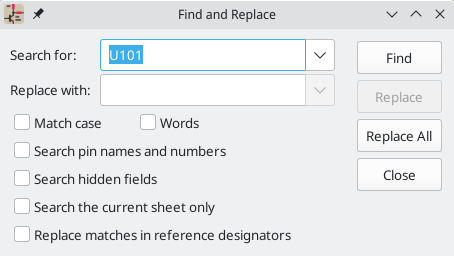

There is also a Find and Replace tool which is activated with the ![]() button in the top toolbar. This tool behaves the same as the Find tool, but additionally can replace some or all matches with different text.

button in the top toolbar. This tool behaves the same as the Find tool, but additionally can replace some or all matches with different text.

If the Replace matches in reference designators option is checked, reference designators will be modified if they contain matching text. Otherwise reference designators will not be affected.

Net highlighting

An electrical net can be highlighted in the schematic editor to visualize all of the places it appears in the schematic. Net highlighting can be activated in the Schematic Editor or by highlighting the corresponding net in the PCB editor when cross-probe highlighting is enabled (see below). When net highlighting is active, the highlighted net will be shown in a different color. By default this color is pink, but it is configurable in the Color section of the Preferences dialog.

Nets can be highlighted by clicking on a wire or pin using the Highlight Net tool in the right toolbar (![]() ). Alternatively, the Highlight Net hotkey (`) highlights the net under the cursor. If there are no nets or pins under the cursor, any existing highlighting will be cleared. The highlighting can also be cleared by using the Clear Net Highlight action (hotkey ~).

). Alternatively, the Highlight Net hotkey (`) highlights the net under the cursor. If there are no nets or pins under the cursor, any existing highlighting will be cleared. The highlighting can also be cleared by using the Clear Net Highlight action (hotkey ~).

Cross-probing from the PCB

KiCad allows bi-directional cross-probing between the schematic and the PCB. There are several different types of cross-probing.

Selection cross-probing allows you to select a symbol or pin in the schematic to select the corresponding footprint or pad in the PCB (if one exists) and vice-versa. By default, cross-probing will result in the display centering on the cross-probed item and zooming to fit. This behavior can be disabled in the Display Options section of the Preferences dialog.

Highlight cross-probing allows you to highlight a net in the schematic and PCB at the same time. If the option "Highlight cross-probed nets" is enabled in the Display Options section of the Preferences dialog, highlighting a net or bus in the schematic editor will cause the corresponding net or nets to be highlighted in the PCB editor, and vice versa.

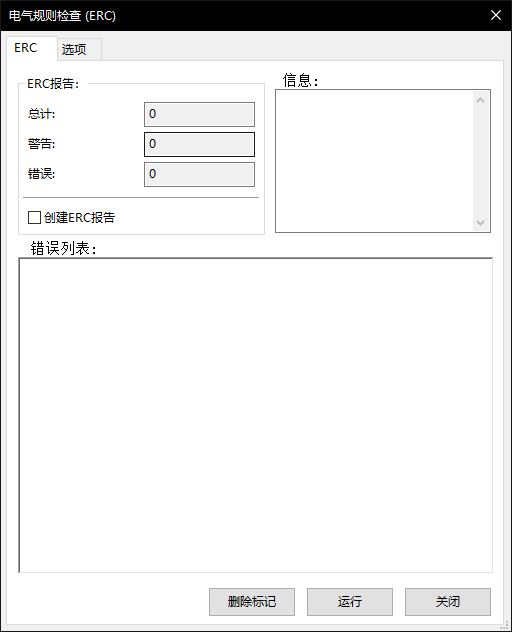

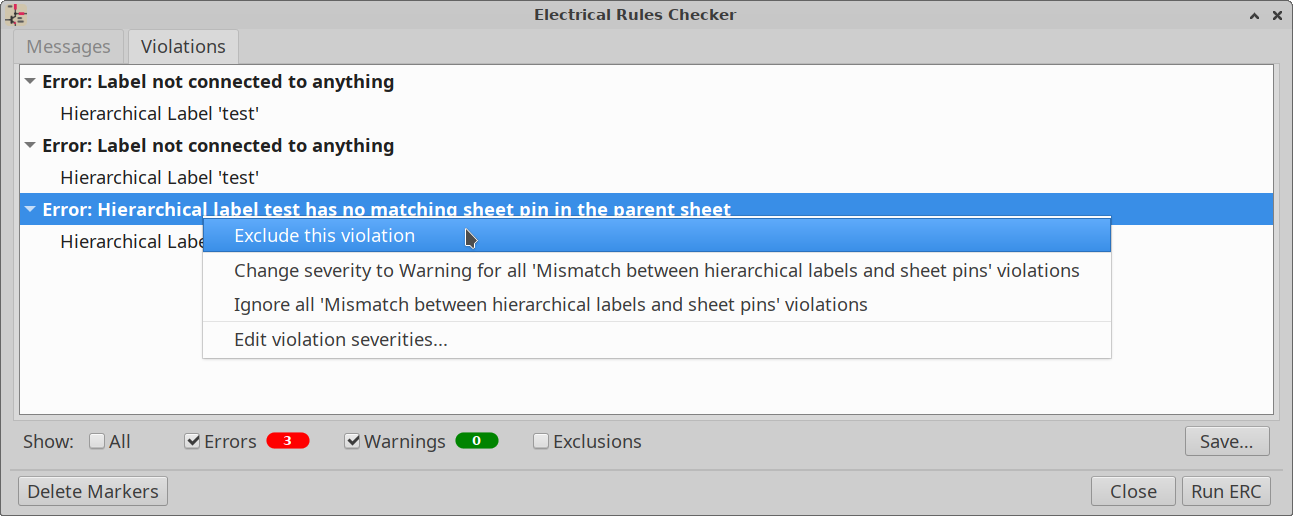

使用电气规则检查进行设计验证

The Electrical Rules Check (ERC) tool performs an automatic check of your schematic. The ERC checks for any errors in your sheet, such as unconnected pins, unconnected hierarchical symbols, shorted outputs, etc. ERC output is reported as errors or warnings depending on the severity of the issue detected.

Naturally, an automatic check is not infallible, and it is not possible to detect all design errors. Such a check is still very useful, because it allows you to detect many oversights and small errors. All detected issues should be checked and addressed before proceeding.

The quality of the ERC is directly related to the care taken in declaring electrical pin properties during symbol library creation.

ERC can be started by clicking on the ![]() button in the top toolbar and clicking the Run ERC button.

button in the top toolbar and clicking the Run ERC button.

Any warnings or errors are reported in the Violations tab, and markers for each violation are placed in the schematic so that they point to the relevant part of the schematic. Warnings are indicated by yellow arrows, and errors have red arrows. Excluded violations are shown as green arrows.

| Selecting a violation in the ERC window jumps to the selected violation marker in the schematic. |

The numbers at the bottom of the window show the number of errors, warnings, and exclusions. Each type of violation can be filtered from the list using the respective checkboxes. Clicking Delete Markers will clear all violations until ERC is run again.

Violations can be right-clicked in the dialog to ignore them or change their severity:

-

Exclude this violation: ignores this particular violation, but does not affect any other violations.

-

Change severity: changes a type of violation from warning to error, or error to warning. This affects all violations of a given type.

-

Ignore all: ignores all violations of a given type.

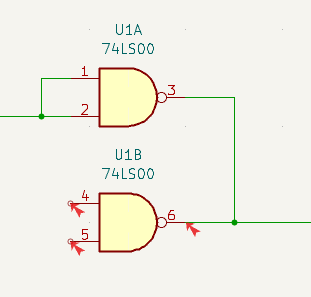

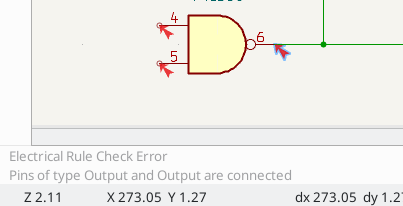

ERC example

Here you can see three errors:

-

Two outputs have been connected together (red arrow at right).

-

Two inputs have been left unconnected (red arrows at left).

Selecting an ERC marker displays a description of the violation in the message pane at the bottom of the window.

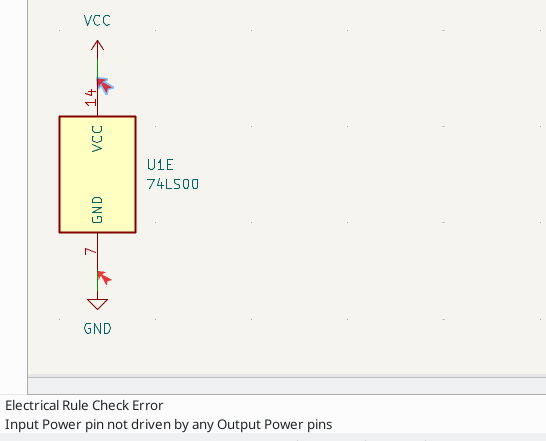

Power pins and power flags

It is common to have an "Input Power pin not driven by any Output Power pins" error on power pins, as shown in the example below, even though the power pins seem to be properly connected to a power rail. This happens in designs where the power is provided through connectors or other components that are not marked as power outputs. In these cases ERC won’t detect any Output Power pins connected to the net and will determine the Input Power pin is not driven by a power source.

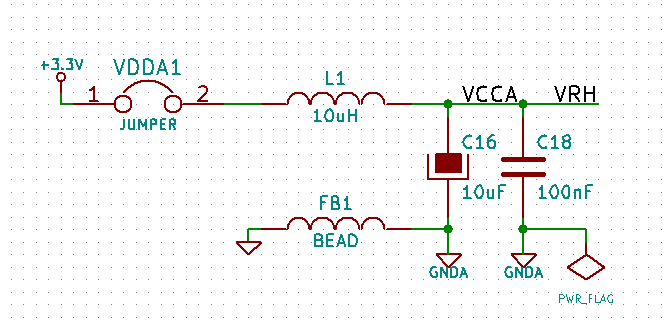

To avoid this warning, connect the net to PWR_FLAG symbol on such a power net as shown in the following example. The PWR_FLAG symbol is found in the power symbol library. Alternatively, connect any power output pin to the net; PWR_FLAG is simply a symbol with a single power output pin.

Ground nets often need a PWR_FLAG as well, because voltage regulators have outputs declared as power outputs, but their ground pins are typically marked as power inputs. Therefore grounds can appear unconnected to a source unless a PWR_FLAG symbol is used.

For more information about power pins and power flags, see the PWR_FLAG documentation.

ERC Configuration

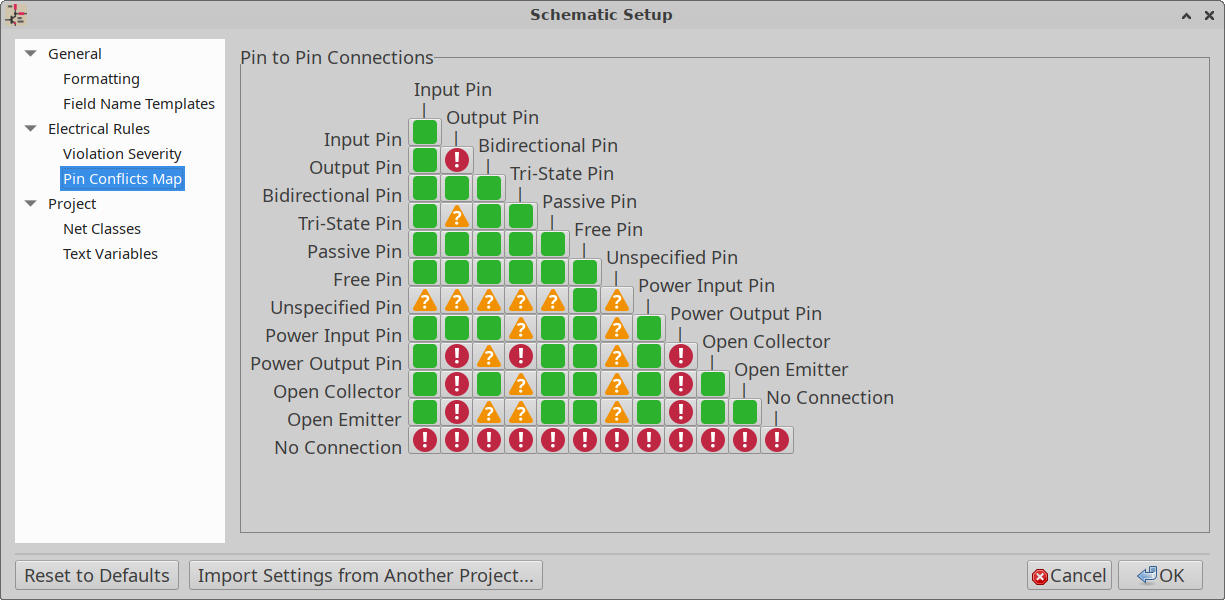

The Pin Conflicts Map panel in Schematic Setup allows you to configure connectivity rules to define electrical conditions for errors and warnings based on what types of pins are connected to each other.

单击所需的单元格方块可以更改规则,使其循环选择:正常,警告,错误。

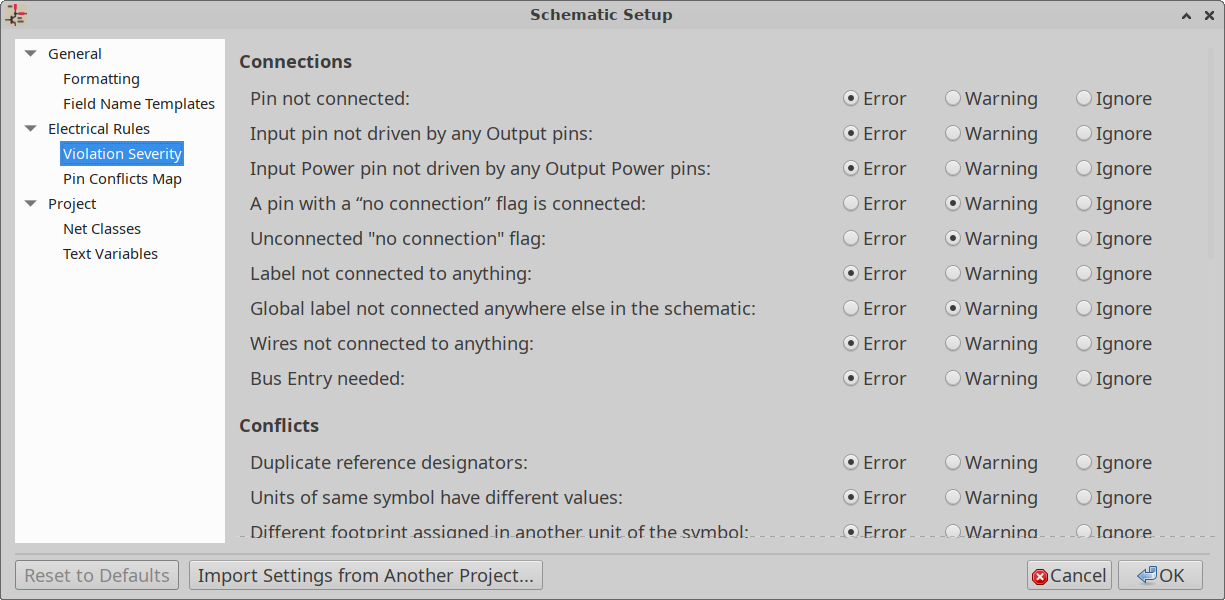

The Violation Severity panel in Schematic Setup lets you configure what types of ERC messages should be reported as Errors, Warnings or ignored.

ERC 报告文件

An ERC report file can be generated and saved by clicking the Save… button in the ERC dialog. The file extension for ERC report files is .rpt. Here is an example ERC report file.

ERC report (Fri 21 Oct 2022 02:07:05 PM EDT, Encoding UTF8)

***** Sheet /

[pin_not_driven]: Input pin not driven by any Output pins

; Severity: error

@(149.86 mm, 60.96 mm): Symbol U1B [74LS00] Pin 4 [, Input, Line]

[pin_not_connected]: Pin not connected

; Severity: error

@(149.86 mm, 60.96 mm): Symbol U1B [74LS00] Pin 4 [, Input, Line]

[pin_not_connected]: Pin not connected

; Severity: error

@(149.86 mm, 66.04 mm): Symbol U1B [74LS00] Pin 5 [, Input, Line]

[pin_to_pin]: Pins of type Output and Output are connected

; Severity: error

@(165.10 mm, 63.50 mm): Symbol U1B [74LS00] Pin 6 [, Output, Inverted]

@(165.10 mm, 46.99 mm): Symbol U1A [74LS00] Pin 3 [, Output, Inverted]

[pin_not_driven]: Input pin not driven by any Output pins

; Severity: error

@(149.86 mm, 66.04 mm): Symbol U1B [74LS00] Pin 5 [, Input, Line]

** ERC messages: 5 Errors 5 Warnings 0

Assigning Footprints

Before routing a PCB, footprints need to be selected for every component that will be assembled on the board. Footprints define the copper connections between physical components and the routed traces on a circuit board.

Some symbols come with footprints pre-assigned, but for many symbols there are multiple possible footprints, so the user needs to select the appropriate one.

KiCad offers several ways to assign footprints:

-

符号属性

-

Symbol Properties Dialog

-

Symbol Fields Table

-

-

While placing symbols

-

Footprint Assignment Tool

Each method will be explained below. Which to use is a matter of preference; one method may be more convenient depending on the situation. All of these methods are equivalent in that they store the name of the selected footprint in the symbol’s Footprint field.

| The Footprint Library Table needs to be configured before footprints can be assigned. For information on configuring the Footprint Library Table, please see the PCB Editor manual. |

Assigning Footprints in Symbol Properties

A symbol’s Footprint field can be edited directly in the symbol’s Properties window.

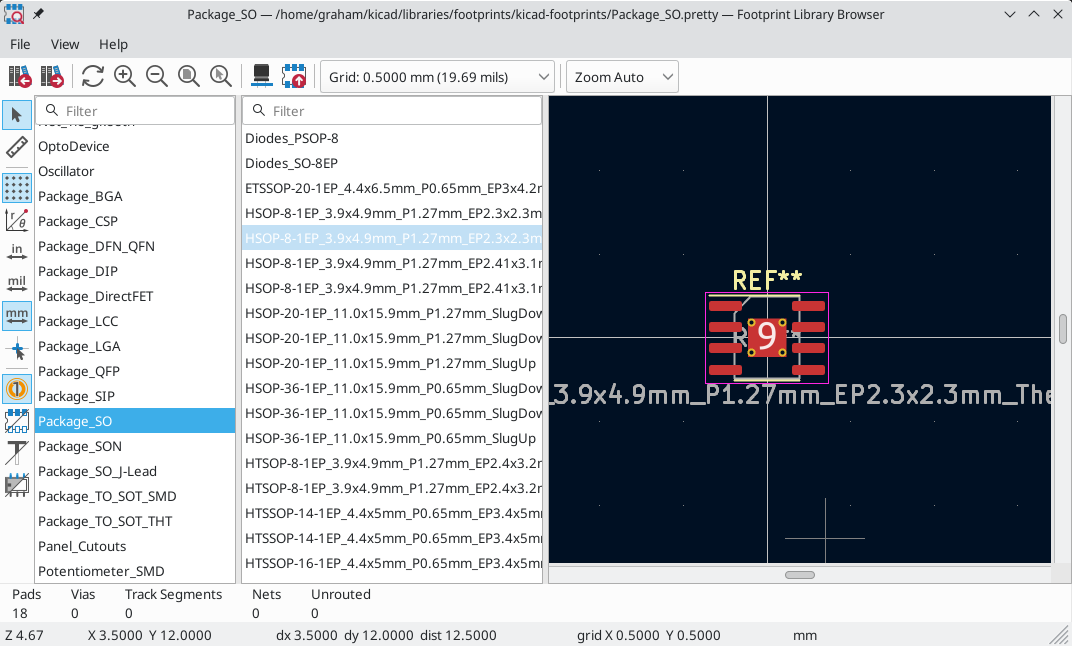

Clicking the ![]() button in the

button in the Footprint field opens the Footprint Library Browser, which shows the available footprints and footprint libraries. Single clicking a footprint name selects the footprint and displays it in the preview pane on the right, while double clicking on a footprint closes the browser and sets the symbol’s Footprint field to the selected footprint.

Assigning Footprints with the Symbol Fields Table

Rather than editing the properties of each symbol individually, the Symbol Fields Table can be used to view and edit the properties of all symbols in the design in one place. This includes assigning footprints by editing the Footprint field of each symbol.

The Symbol Fields Table is accessed with Tools → Edit Symbol Fields…, or with the ![]() button on the top toolbar.

button on the top toolbar.

The Footprint field behaves the same here as in the Symbol Properties window: it can be edited directly, or footprints can be selected visually with the Footprint Library Browser.

For more information on the Symbol Fields Table, see the section on editing symbol properties.

Assigning Footprints While Placing Symbols

Footprints can be assigned to symbols when the symbol is first added to the schematic.

Some symbols are defined with a default footprint. These symbols will have this footprint preassigned when they are added to the schematic. The default footprint is shown in the Add Symbol dialog. For symbols without a default symbol defined, the footprint dropdown will say "No default footprint", and the footprint preview canvas will say "No footprint specified".

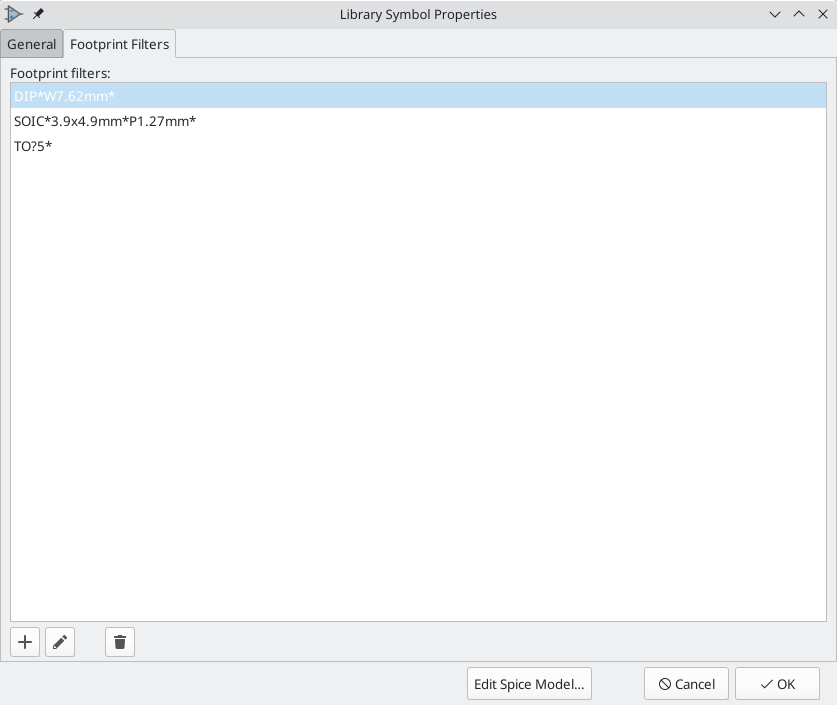

Symbols can have footprint filters that specify which footprints are appropriate to use with that symbol. If footprint filters are defined for the selected symbol, all footprints that match the footprint filters will appear as options in the footprint dropdown. The selected footprint will be displayed in the preview canvas and will be assigned to the symbol when the symbol is added to the schematic.

| Footprint options will not appear in the footprint dropdown unless the footprint libraries are loaded. Footprint libraries are loaded the first time the Footprint Editor or Footprint Library Browser are opened in a session. |

For more information on footprint filters, see the Symbol Editor Documentation.

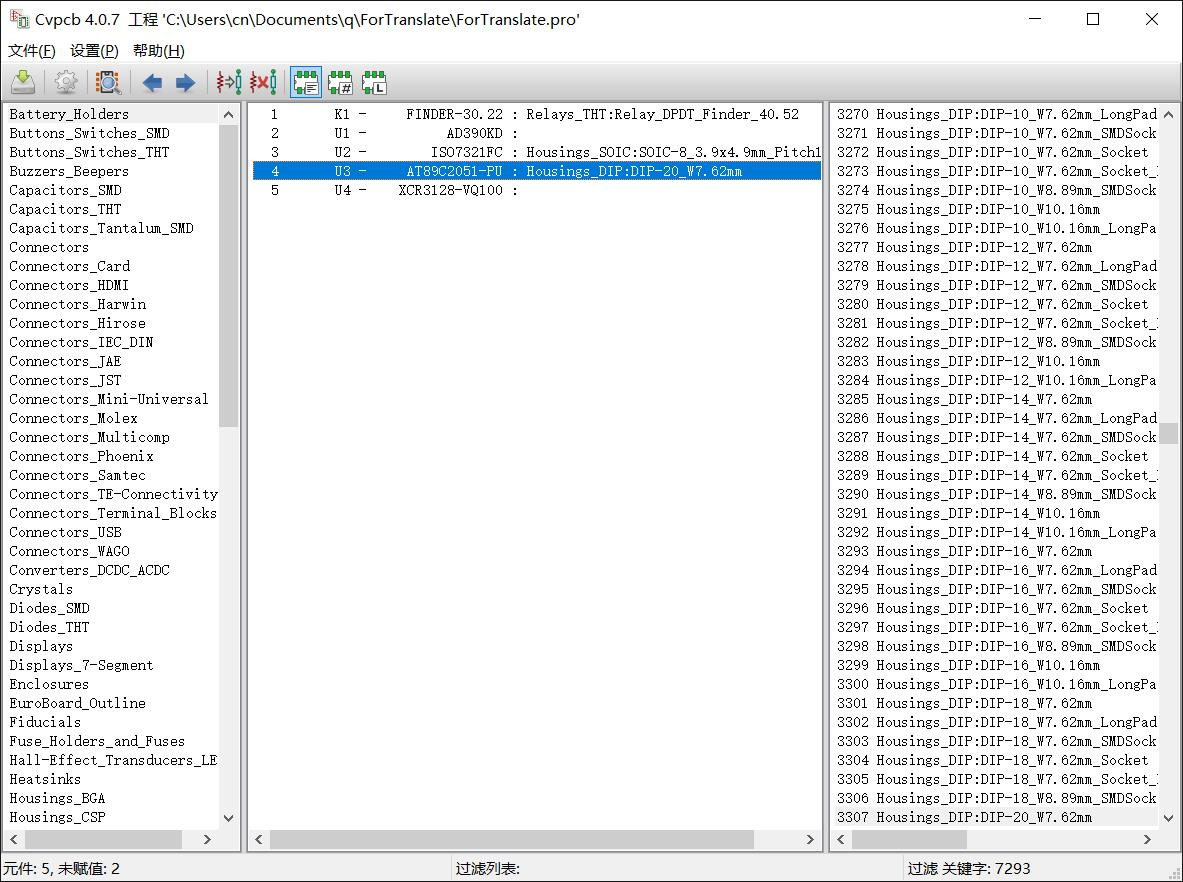

Assigning Footprints with the Footprint Assignment Tool

The Footprint Assignment Tool allows you to associate symbols in your schematic to footprints used when laying out the printed circuit board. It provides footprint list filtering, footprint viewing, and 3D component model viewing to help ensure the correct footprint is associated with each component.

Components can be assigned to their corresponding footprints manually or automatically by creating equivalence files (.equ files). Equivalence files are lookup tables associating each component with its footprint.

Run the tool with Tools → Assign Footprints…, or by clicking the ![]() icon in the top toolbar.

icon in the top toolbar.

Footprint Assignment Tool Overview

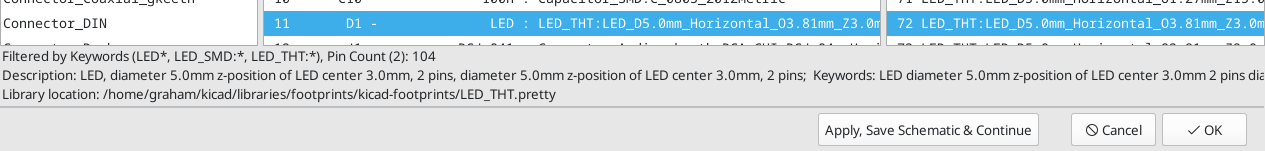

The image below shows the main window of the Footprint Assignment Tool.

-

The left pane contains the list of available footprint libraries associated with the project.

-

The center pane contains the list of symbols in the schematic.

-

The right pane contains the list of available footprints loaded from the project footprint libraries.

-

The bottom pane describes the filters that have been applied to the footprint list and prints information about the footprint selected in the rightmost pane.

The top toolbar contains the following commands:

|

Transfer the current footprint associations to the schematic. |

|

Edit the global and project footprint library tables. |

|

View the selected footprint in the footprint viewer. |

|

Select the previous symbol without a footprint association. |

|

Select the next symbol without a footprint association. |

|

Undo last edit. |

|

Redo last edit. |

|

Perform automatic footprint association using an equivalence file. |

|

Delete all footprint assignments. |

|

Filter footprint list by footprint filters defined in the selected symbol. |

|

Filter footprint list by pin count of the selected symbol. |

|

Filter footprint list by selected library. |

The following table lists the keyboard commands for the Footprint Assignment Tool:

Right Arrow / Tab |

Activate the pane to the right of the currently activated pane. Wrap around to the first pane if the last pane is currently activated. |

Left Arrow |

Activate the pane to the left of the currently activated pane. Wrap around to the last pane if the first pane is currently activated. |

Up Arrow |

Select the previous item of the currently selected list. |

Down Arrow |

Select the next item of the currently selected list. |

Page Up |

Select the item one full page upwards of the currently selected item. |

Page Down |

Select the item one full page downwards of the currently selected item. |

Home |

Select the first item of the currently selected list. |

End |

Select the last item of the currently selected list. |

Manually Assigning Footprints with the Footprint Assignment Tool

To manually associate a footprint with a component, first select a component in the component (middle) pane. Then select a footprint in the footprint (right) pane by double-clicking on the name of the desired footprint. The footprint will be assigned to the selected component, and the next component without an assigned footprint is automatically selected.

| If no footprints appear in the footprint pane, check that the footprint filter options are correctly applied. |

When all components have footprints assigned to them, click the OK button to save the assignments and exit the tool. Alternatively, click Cancel to discard the updated assignments, or Apply, Save Schematic & Continue to save the new assignments without exiting the tool.

过滤封装列表

There are four filtering options which restrict which footprints are displayed in the footprint pane. The filtering options are enabled and disabled with three buttons and a textbox in the top toolbar.

-

: Activate filters that can be defined in each symbol. For example, an opamp symbol might define filters that show only SOIC and DIP footprints.

: Activate filters that can be defined in each symbol. For example, an opamp symbol might define filters that show only SOIC and DIP footprints. -

: Only show footprints that match the selected symbol’s pin count.

: Only show footprints that match the selected symbol’s pin count. -

: Only show footprints from the library selected in the left pane.

: Only show footprints from the library selected in the left pane. -

Entering text in the textbox hides footprints that do not match the text. This filter is disabled when the box is empty.

When all filters are disabled, the full footprint list is shown.

The applied filters are described in the bottom pane of the window, along with the number of footprints that meet the selected filters. For example, when the symbol’s footprint filters and pin count filters are enabled, the bottom pane prints the footprint filters and pin count:

Multiple filters can be used at once to help narrow down the list of possibly appropriate footprints in the footprint pane. The symbols in KiCad’s standard library define footprint filters that are designed to be used in combination with the pin count filter.

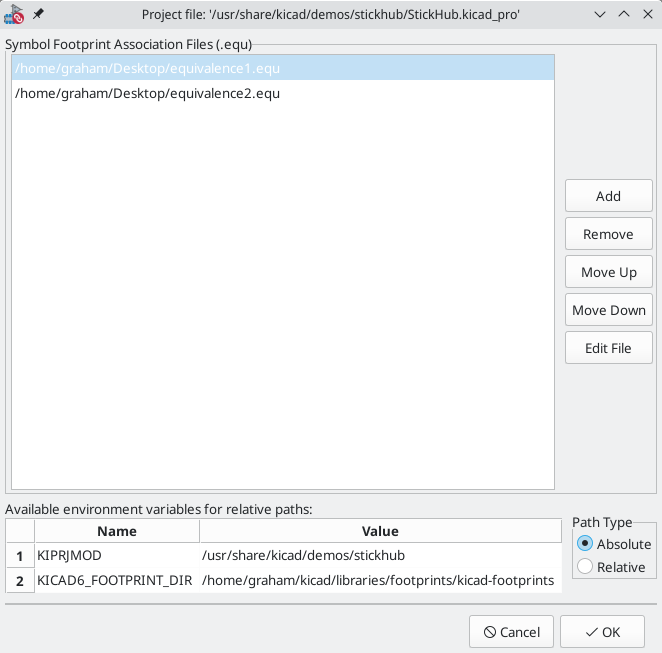

Automatically Assigning Footprints with the Footprint Assignment Tool

The Footprint Assignment Tool allows you to store footprint assignments in an external file and load the assignments later, even in a different project. This allows you to automatically associate symbols with the appropriate footprints.

The external file is referred to as an equivalence file, and it stores a mapping of a symbol value to a corresponding footprint. Equivalence files typically use the .equ file extension. Equivalence files are plain text files with a simple syntax, and must be created by the user using a text editor. The syntax is described below.

You can select which equivalence files to use by clicking Preferences → Manage Footprint Association Files in the Footprint Assignment Tool.

-

Add new equivalence files by clicking the Add button.

-

Remove the selected equivalence file by clicking the Remove button.

-

Change the priority of equivalence files by clicking the Move Up and Move Down buttons. If a symbol’s value is found in multiple equivalence files, the footprint from the last matching equivalence file will override earlier equivalence files.

-

Open the selected equivalence file by clicking the Edit File button.

Relevant environment variables are shown at the bottom of the window. When the Relative path option is checked, these environment variables will automatically be used to make paths to selected equivalence files relative to the project or footprint libraries.

Once the desired equivalence files have been loaded in the correct order, automatic footprint association can be performed by clicking the ![]() button in the top toolbar of the Footprint Assignment Tool.

button in the top toolbar of the Footprint Assignment Tool.

All symbols with a value found in a loaded equivalence file will have their footprints automatically assigned. However, symbols that already have footprints assigned will not be updated.

Equivalence 文件格式

Equivalence files consist of one line for each symbol value. Each line has the following structure:

'<symbol value>' '<footprint library>:<footprint name>'

Each name/value must be surrounded by single quotes (') and separated by one or more spaces. Lines starting with # are comments.

For example, if you want all symbols with the value LM4562 to be assigned the footprint Package_SO:SOIC-8_3.9x4.9_P1.27mm, the line in the equivalence file should be:

'LM4562' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm'

Equivalence 文件示例:

#integrated circuits (smd): '74LV14' 'Package_SO:SOIC-14_3.9x8.7mm_P1.27mm' 'EL7242C' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'DS1302N' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LM324N' 'Package_SO:SOIC-14_3.9x8.7mm_P1.27mm' 'LM358' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LTC1878' 'Package_SO:MSOP-8_3x3mm_P0.65mm' '24LC512I/SM' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LM2903M' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LT1129_SO8' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LT1129CS8-3.3' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LT1129CS8' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'LM358M' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'TL7702BID' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'TL7702BCD' 'Package_SO:SOIC-8_3.9x4.9_P1.27mm' 'U2270B' 'Package_SO:SOIC-16_3.9x9.9_P1.27mm' #regulators 'LP2985LV' 'Package_TO_SOT_SMD:SOT-23-5_HandSoldering'

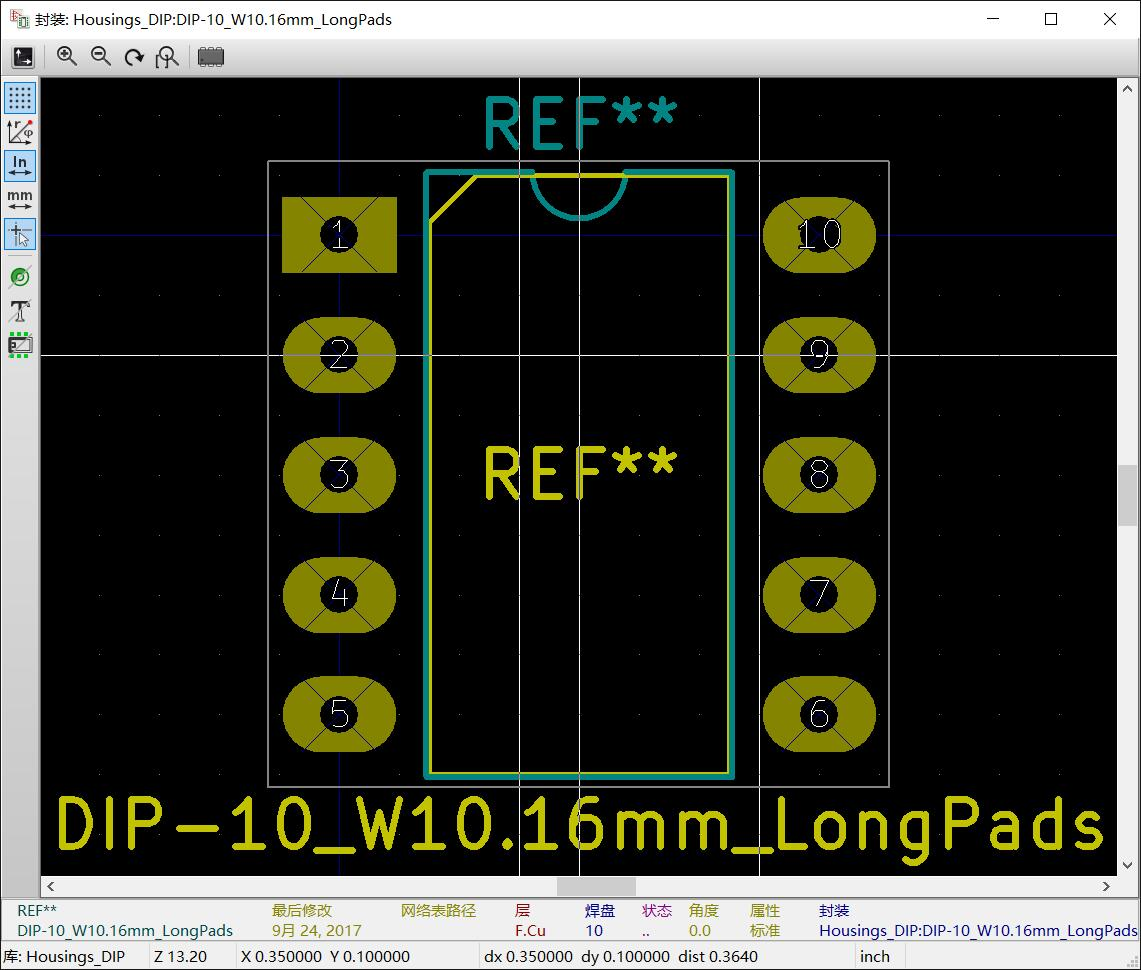

查看当前封装

The Footprint Assignment Tool contains a footprint viewer. Clicking the ![]() button in the top toolbar launches the footprint viewer and shows the selected footprint.

button in the top toolbar launches the footprint viewer and shows the selected footprint.

The top toolbar contains the following commands:

|

Refresh view |

|

Zoom in |

|

Zoom out |

|

Zoom to fit drawing in display area |

|

Show 3D viewer |

The left toolbar contains the following commands:

|

Use the select tool |

|

Interactively measure between two points |

|

Display grid dots or lines |

|

Switch between polar and cartesian coordinate systems |

|

Use inches |

|

Display coordinates in mils (1/1000 of an inch) |

|

Display coordinates in millimeters |

|

Toggle display of full-window crosshairs |

|

Toggle between drawing pads in sketch or normal mode |

|

Toggle between drawing pads in normal mode or outline mode |

|

Toggle between drawing text in normal mode or outline mode |

|

Toggle between drawing graphic lines in normal mode or outline mode |

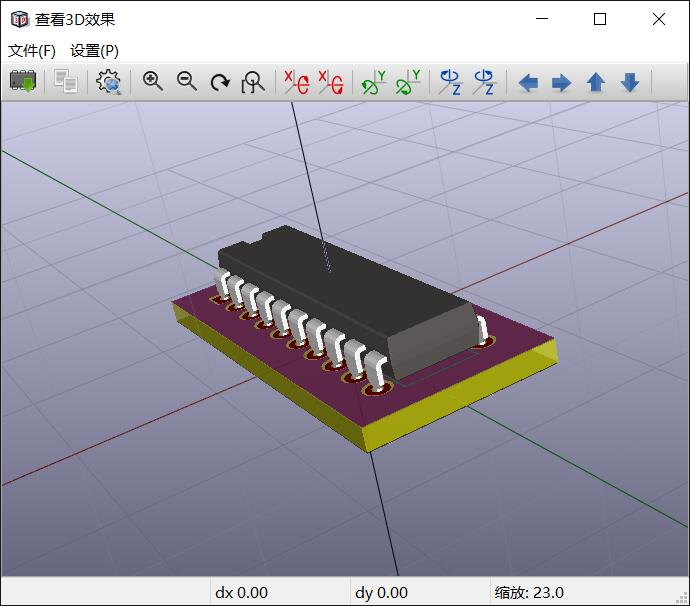

查看当前 3D 模型

Clicking the ![]() button opens the footprint in the 3D model viewer.

button opens the footprint in the 3D model viewer.

| If a 3D model does not exist for the current footprint, only the footprint itself will be shown in the 3D Viewer. |

The 3D Viewer is described in the PCB Editor manual.

Transferring designs between schematic and PCB

Update PCB from Schematic

Use the Update PCB from Schematic tool to sync design information from the Schematic Editor to the Board Editor. The tool can be accessed with Tools → Update PCB from Schematic (F8) in both the schematic and board editors. You can also use the ![]() icon in the top toolbar of the Board Editor.

icon in the top toolbar of the Board Editor.

| Update PCB from Schematic is the preferred way to transfer design information from the schematic to the PCB. In older versions of KiCad, the equivalent process was to export a netlist from the Schematic Editor and import it into the Board Editor. It is no longer necessary to use a netlist file. |

The tool adds the footprint for each symbol to the board and transfers updated schematic information to the board. In particular, the board’s net connections are updated to match the schematic.

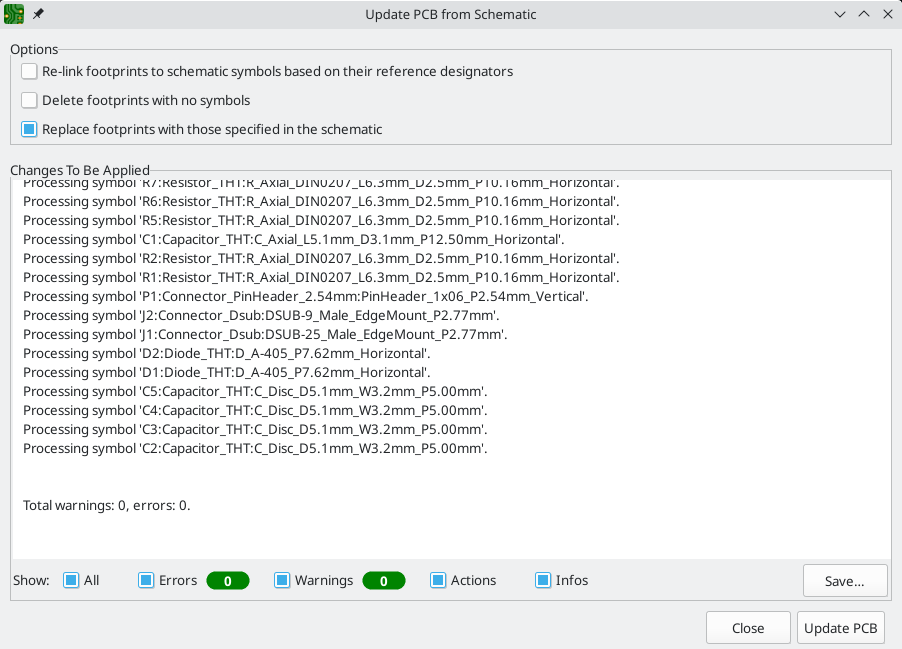

The changes that will be made to the PCB are listed in the Changes To Be Applied pane. The PCB is not modified until you click the Update PCB button.

You can show or hide different types of messages using the checkboxes at the bottom of the window. A report of the changes can be saved to a file using the Save… button.

Options

The tool has several options to control its behavior.

| Option | Description |

|---|---|

Re-link footprints to schematic symbols based on their reference designators |

Footprints are normally linked to schematic symbols via a unique identifier created when the symbol is added to the schematic. A symbol’s unique identifier cannot be changed. If checked, each footprint in the PCB will be re-linked to the symbol that has the same reference designator as the footprint. If unchecked, footprints and symbols will be linked by unique identifier as usual, rather than by reference designator. Each footprint’s reference designator will be updated to match the reference designator of its linked symbol. This option should generally be left unchecked. It is useful for specific workflows that rely on changing the links between schematic symbols and footprints, such as refactoring a schematic for easier layout or replicating layout between identical channels of a design. |

Delete footprints with no symbols |

If checked, any footprint in the PCB without a corresponding symbol in the schematic will be deleted from the PCB. Footprints with the "Not in schematic" attribute will be unaffected. If unchecked, footprints without a corresponding symbol will not be deleted. |

Replace footprints with those specified in the schematic |

If checked, footprints in the PCB will be replaced with the footprint that is specified in the corresponding schematic symbol. If unchecked, footprints that are already in the PCB will not be changed, even if the schematic symbol is updated to specify a different footprint. |

Update Schematic from PCB

| TODO: write this section |

Backannotation with CMP files

Select changes can also be synced from the PCB back to the schematic by exporting a CMP file from the PCB editor (File → Export → Footprint Association (.cmp) File…) and importing it in the Schematic Editor (File → Import → Footprint Assignments…).

| This method can only sync changes made to footprint assignments and footprint fields. It is recommended to use the Update Schematic from PCB tool instead. |

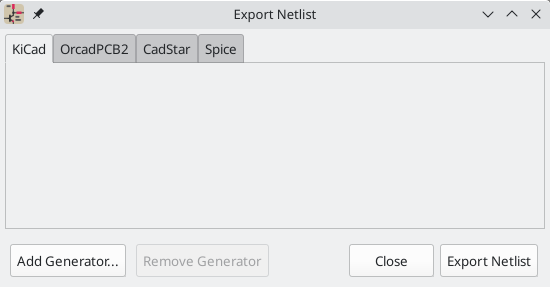

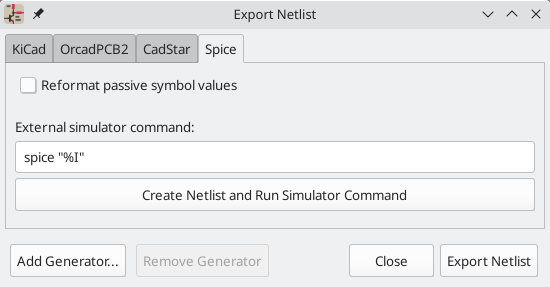

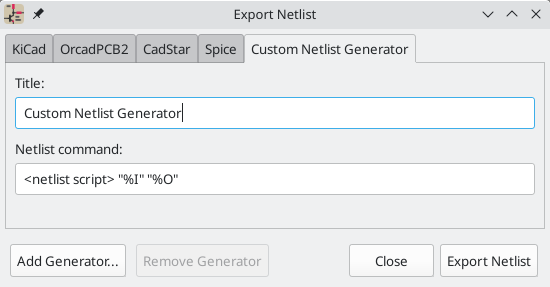

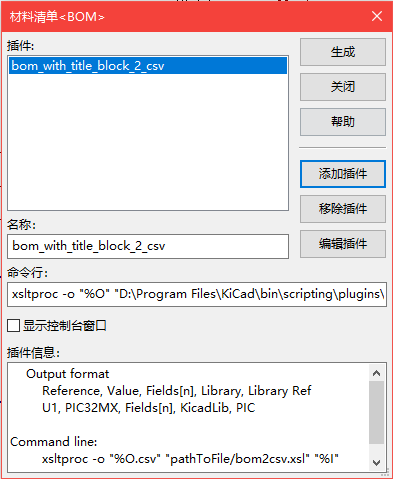

Generating Outputs

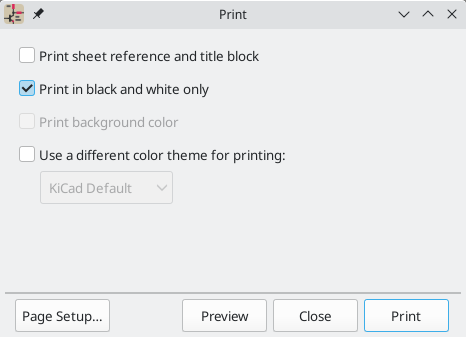

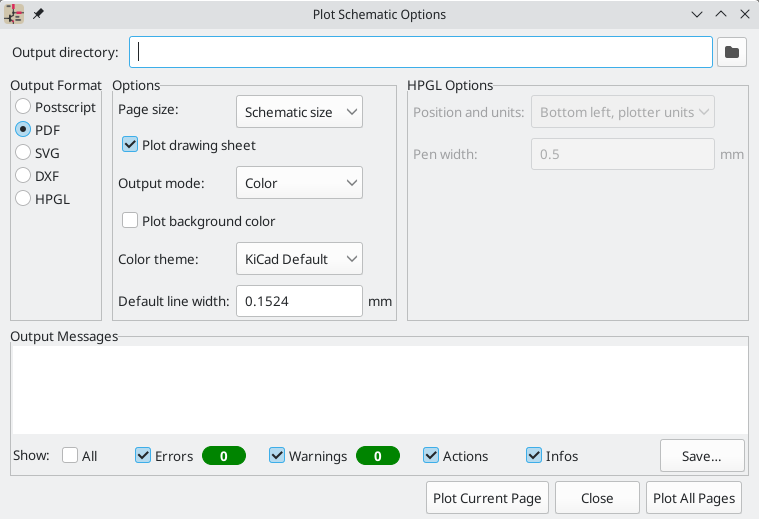

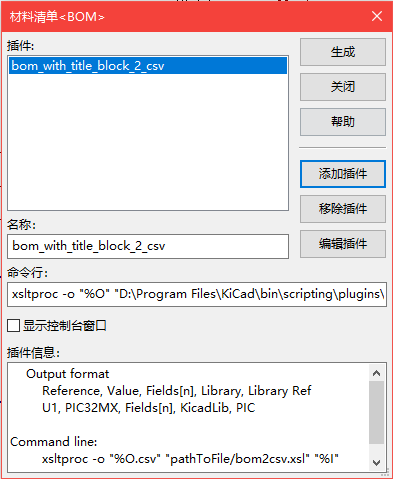

Printing