KiCad Nightly Reference Manual

| This manual is in the process of being revised to cover the latest stable release version of KiCad. It contains some sections that have not yet been completed. We ask for your patience while our volunteer technical writers work on this task, and we welcome new contributors who would like to help make KiCad’s documentation better than ever. |

Copyright

This document is Copyright The KiCad Documentation Contributors. You may distribute it and/or modify it under the terms of either the GNU General Public License (http://www.gnu.org/licenses/gpl.html), version 3 or later, or the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/), version 3.0 or later.

All trademarks within this guide belong to their legitimate owners.

Contributors

Jean-Pierre Charras, Fabrizio Tappero, Wayne Stambaugh, Graham Keeth

Feedback

The KiCad project welcomes feedback, bug reports, and suggestions related to the software or its documentation. For more information on how to submit feedback or report an issue, please see the instructions at https://www.kicad.org/help/report-an-issue/

Software and Documentation Version

This user manual is based on KiCad 10.99. Functionality and appearance may be different in other versions of KiCad.

Documentation revision: a87cc139.

Introduction to the KiCad Schematic Editor

The KiCad Schematic Editor is a schematic capture application distributed as a part of KiCad and available for the following operating systems:

-

Linux

-

Apple macOS

-

Windows

Regardless of the OS, all KiCad files are 100% compatible from one OS to another.

The Schematic Editor is an integrated application where all functions of schematic drawing, PCB footprint selection, library management, and data transfer to and from the PCB design software are carried out within the editor itself.

The KiCad Schematic Editor is intended to communicate directly with the KiCad PCB Editor for designing printed circuit boards without using any intermediate files. It can also export netlist files, which list all the electrical connections, for other packages.

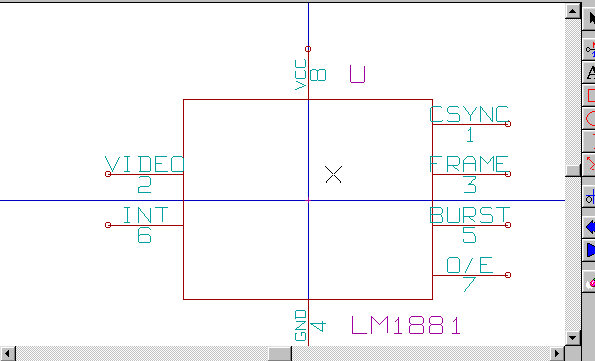

The Schematic Editor includes a symbol library editor, which can create and edit symbols and manage libraries. It also integrates the following additional but essential functions needed for modern schematic capture software:

-

Electrical rules check (ERC) for automatic detection of incorrect and missing connections

-

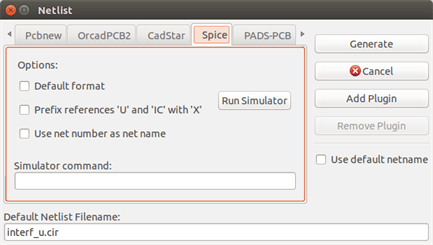

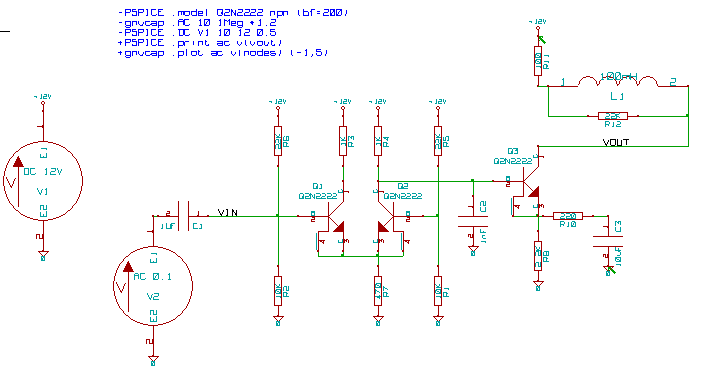

Circuit simulation using ngspice

-

Export of plot files in many formats (Postscript, PDF, HPGL, and SVG)

-

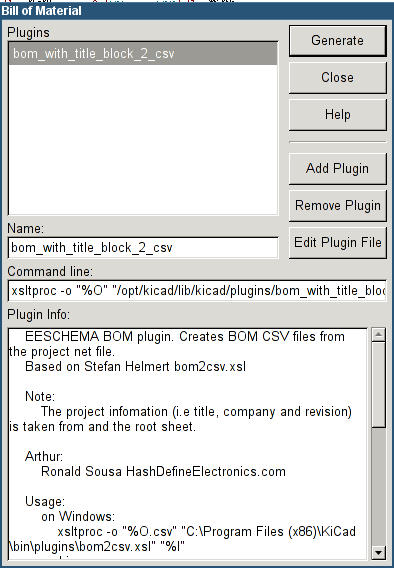

Bill of Materials generation (via Python or XSLT scripts, which allow many flexible formats).

The Schematic Editor supports multi-sheet schematics in several ways:

-

Flat hierarchies (schematic sheets are not explicitly connected in a master diagram).

-

Simple hierarchies (each schematic sheet is used only once).

-

Complex hierarchies (some schematic sheets are used multiple times).

Hierarchical schematics are described in detail later in the manual.

The Schematic Editor User Interface

The main Schematic Editor user interface is shown above, with some key elements indicated:

-

Top toolbars (file management, zoom tools, editing tools)

-

Message panel and status bar

-

Editing canvas

Navigating the editing canvas

The editing canvas displays the schematic being designed. You can pan and zoom to different parts of the schematic and open any schematic sheet in the design.

By default, dragging with the middle or right mouse button will pan the canvas view and scrolling the mouse wheel will zoom the view in or out. You can change this behavior in the Mouse and Touchpad section of the preferences (see Configuration and Customization for details).

Several other zoom tools are available in the top toolbar:

-

zooms in on the center of the

viewport.

zooms in on the center of the

viewport. -

zooms out from the center of

the viewport.

zooms out from the center of

the viewport. -

zooms to fit the

frame around the drawing sheet.

zooms to fit the

frame around the drawing sheet. -

zooms to

fit every item in the schematic (not including the drawing sheet). For

instance, if there are items placed outside of the drawing sheet, they will be

visible after zooming to objects.

zooms to

fit every item in the schematic (not including the drawing sheet). For

instance, if there are items placed outside of the drawing sheet, they will be

visible after zooming to objects. -

allows you to

draw a box to determine the zoomed area.

allows you to

draw a box to determine the zoomed area.

The cursor’s current position is displayed at the bottom of the window (X and Y), along with the current zoom factor (Z), the cursor’s relative position (dx, dy, and dist), the grid setting, and the display units.

The relative coordinates can be reset to zero by pressing Space. This is useful for measuring distance between two points or aligning objects.

Hotkeys

The Ctrl+F1 shortcut displays the current hotkey list. The default hotkey list is included in the Actions Reference section of the manual.

The hotkeys described in this manual use the key labels that appear on a standard PC keyboard. On an Apple keyboard layout, use the Cmd key in place of Ctrl, and the Option key in place of Alt.

Many actions do not have hotkeys assigned by default, but hotkeys can be assigned or redefined using the hotkey editor (Preferences → Preferences… → Hotkeys).

| Many of the actions available through hotkeys are also available in context menus. To access the context menu, right-click in the editing canvas. Different actions will be available depending on what is selected or what tool is active. |

Hotkeys are stored in the file user.hotkeys in KiCad’s configuration

directory. The location is platform-specific:

-

Windows:

%APPDATA%\kicad\10.0\user.hotkeys -

Linux:

~/.config/kicad/10.0/user.hotkeys -

macOS:

~/Library/Preferences/kicad/10.0/user.hotkeys

KiCad can import hotkey settings from a user.hotkeys file using the Import

Hotkeys button in the hotkey editor.

Selection and the selection filter

Selecting items in the editing canvas is done with the left mouse button. When no tool is active, single-clicking on an object will select it. Pressing Esc will always cancel the current tool or operation and return to the selection tool. Pressing Esc while the selection tool is active will clear the current selection.

You can also select items using a rectangle or lasso selection.

These tools can be useful for selecting many items at once.

You can switch between rectangular and lasso selection modes using the ![]() /

/ ![]() palette in the right toolbar.

palette in the right toolbar.

| To switch between multiple tools in a palette, show the palette by clicking and holding the left mouse button on the tool icon or by clicking and dragging the mouse from the tool icon. Release the mouse button on the desired tool to choose it. |

With the rectangular selection mode active (![]() ),

clicking and dragging will perform a rectangular selection.

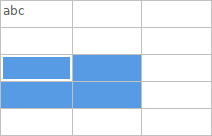

A rectangular selection from left to right will only select items that are fully inside the box.

A rectangular selection from right to left will select any items that touch the box.

A left-to-right selection box is drawn in yellow, with a cursor that indicates exclusive selection,

and a right-to-left selection box is drawn in blue with a cursor that indicates inclusive selection.

),

clicking and dragging will perform a rectangular selection.

A rectangular selection from left to right will only select items that are fully inside the box.

A rectangular selection from right to left will select any items that touch the box.

A left-to-right selection box is drawn in yellow, with a cursor that indicates exclusive selection,

and a right-to-left selection box is drawn in blue with a cursor that indicates inclusive selection.

With the lasso selection mode active (![]() ),

clicking and dragging will begin a lasso selection.

Any items in the existing selection are deselected.

Dragging with the left mouse button held draws a freeform shape.

Releasing the button stops drawing the freeform shape and starts drawing a straight line.

Clicking again completes the straight line.

Any number of freeform or straight segments can be drawn by repeatedly clicking or dragging.

Double click to finish drawing the lasso.

Similar to a rectangular selection,

a lasso drawn in a clockwise direction will only select items that are fully inside the lasso.

A lasso drawn in a counter-clockwise direction will select any items that touch the lasso.

A clockwise lasso is drawn in yellow, with a cursor that indicates exclusive selection,

and a counter-clockwise lasso is drawn in blue with a cursor that indicates inclusive selection.

),

clicking and dragging will begin a lasso selection.

Any items in the existing selection are deselected.

Dragging with the left mouse button held draws a freeform shape.

Releasing the button stops drawing the freeform shape and starts drawing a straight line.

Clicking again completes the straight line.

Any number of freeform or straight segments can be drawn by repeatedly clicking or dragging.

Double click to finish drawing the lasso.

Similar to a rectangular selection,

a lasso drawn in a clockwise direction will only select items that are fully inside the lasso.

A lasso drawn in a counter-clockwise direction will select any items that touch the lasso.

A clockwise lasso is drawn in yellow, with a cursor that indicates exclusive selection,

and a counter-clockwise lasso is drawn in blue with a cursor that indicates inclusive selection.

The selection action can be modified by holding modifier keys while clicking or dragging. Modifiers cannot be used with lasso selections.

The following modifier keys apply when clicking to select single items:

| Modifier Keys (Windows) | Modifier Keys (Linux) | Modifier Keys (macOS) | Selection Effect |

|---|---|---|---|

Ctrl |

Ctrl |

Cmd |

Toggle selection. |

Shift |

Shift |

Shift |

Add the item to the existing selection. |

Ctrl+Shift |

Ctrl+Shift |

Cmd+Shift |

Remove the item from the existing selection. |

long click |

long click or Alt |

long click or Option |

Clarify selection from a pop-up menu. |

The following modifier keys apply when dragging to perform a rectangular selection:

| Modifier Keys (Windows) | Modifier Keys (Linux) | Modifier Keys (macOS) | Selection Effect |

|---|---|---|---|

Ctrl |

Ctrl |

Cmd |

Toggle selection. |

Shift |

Shift |

Shift |

Add item(s) to the existing selection. |

Ctrl+Shift |

Ctrl+Shift |

Cmd+Shift |

Remove item(s) from the existing selection. |

The selection filter panel in the lower left corner of the Schematic Editor window controls which types of objects can be selected with the mouse. Turning off selection of unwanted object types makes it easier to select items in a busy schematic.

The All items checkbox is a shortcut to turn the other items on and off. You can right-click any object type in the selection filter to quickly change the filter to only allow selecting that type of object.

If you repeatedly try to select an object whose type is disabled in the selection filter, the selection filter will visually flash the checkbox for that object type as a reminder that selecting that object type is disabled.

Selecting an object displays information about the object in the message panel at the bottom of the window. Double-clicking an object opens a window to edit the object’s properties.

Left toolbar display controls

The left toolbar provides options to change the display of items in the Schematic Editor.

Some toolbar buttons have more than one item available in a palette.

These buttons are indicated with a small arrow in the lower-right corner of the button:

To show the palette, you can click and hold the mouse button on the button or click and drag the mouse. The palette will show the selected item when it is closed.

The default contents of the left toolbar are shown below.

| You can edit the toolbar’s contents in the Toolbar page of the Schematic Editor Preferences. |

|

Turns grid display on/off. Note: by default, hiding the grid does not disable grid snapping. This behavior can be changed in the Display Options section of Preferences. |

|

Turns item-specific grid overrides on/off. |

|

Display/entry of coordinates and dimensions in inches, mils, or millimeters. Clicking the button toggles to the next unit, or you can choose a unit directly by expanding the palette (click and hold/drag). |

|

Switches the cursor crosshair between small, fullscreen, and 45-degree-rotated fullscreen. Clicking the button toggles to the next crosshair type, or you can choose a crosshair directly by expanding the palette (click and hold/drag). |

|

Turns invisible pin display on/off. |

|

Switches the line mode between free angle, 90 degree mode, and 45 degree mode for placement of new wires, buses, and graphical shapes. Clicking the button toggles to the next line mode, or you can choose a line mode directly by expanding the palette (click and hold/drag). You can also toggle between line modes using Shift+Space. |

|

Turns automatic symbol annotation on/off. When on, symbols will have their reference designators automatically set to the lowest available reference when they are added to the schematic. |

|

Opens and closes the docked Hierarchy Navigator panel. |

|

Opens and closes the docked Properties Manager panel. |

Schematic Creation and Editing

Introduction

A schematic designed with KiCad is more than a simple graphic representation of an electronic device. It is normally the entry point of a development chain that allows for:

-

Validating against a set of rules (Electrical Rules Check) to detect errors and omissions.

-

Automatically generating a bill of materials.

-

Generating a netlist for simulation software such as SPICE.

-

Defining a circuit for transferring to PCB layout.

A schematic mainly consists of symbols, wires, labels, junctions, buses and power symbols. For clarity in the schematic, you can place purely graphical elements like bus entries, comments, and polylines.

Symbols are added to the schematic from symbol libraries. After the schematic is made, the set of connections and footprints is imported into the PCB editor for designing a board.

Schematics can be contained in a single sheet or split among multiple sheets. In

KiCad, multi-sheet schematics are organized hierarchically, with a root sheet

and sub-sheet(s). Each sheet is its own .kicad_sch file and is itself a

complete KiCad schematic. Working with hierarchical schematics is described in

the Hierarchical Schematics chapter.

Schematic editing operations

Schematic editing tools are located in the right toolbar. When a tool is activated, it stays active until a different tool is selected or the tool is canceled with the Esc key. The selection tool is always activated when any other tool is canceled.

Some toolbar buttons have more than one tool available in a palette.

These tools are indicated with a small arrow in the lower-right corner of the button:

To show the palette, you can click and hold the mouse button on the button or click and drag the mouse. The palette will show the most recently selected item when it is closed.

The default contents of the right toolbar are shown below.

| You can edit the toolbar’s contents in the Toolbar page of the Schematic Editor Preferences. |

|

Selection tool (the default tool) When the rectangular selection mode is active, clicking and dragging performs a rectangular selection. When the lasso selection mode is active, clicking and dragging performs a lasso selection. Only one selection mode is visible in the toolbar at a time; you can expand the palette to choose another tool by clicking and holding/dragging. |

|

Highlight a net by marking its wires and net labels with a different color. If the PCB Editor is also open then copper corresponding to the selected net will be highlighted as well. Net highlighting can be cleared by clicking with the highlight tool in an empty space, or by using the Clear Net Highlighting hotkey (~). |

|

Display the symbol selector dialog to place a new symbol. |

|

Display the power symbol selector dialog to place a new power symbol. |

|

|

|

|

|

Draw wire-to-bus entry points. These elements are only graphical and do not create a connection, thus they should not be used to connect wires together. |

|

Place a "no-connection" flag. These flags should be placed on symbol pins which are meant to be left unconnected. "No-connection" flags indicate to the Electrical Rule Checker that the pin is intentionally unconnected and not an error. They also affect schematic connectivity for stacked symbol pins. |

|

Place a junction. This connects two crossing wires or a wire and a pin, which can sometimes be ambiguous without a junction (i.e. if a wire end or a pin is not directly connected to another wire end). |

|

Place a local label, directive label, global label, or hierarchical label. Local labels connect items located in the same sheet. Local labels with the same name are connected as long as they are in the same sheet. Global labels connect items located anywhere in the schematic. All global labels with the same name are connected, even when located on different sheets. Hierarchical labels are used to create a connection between a subsheet and the sheet’s parent sheet. See the Hierarchical Schematics section for more information about hierarchical labels, sheets, and pins. Directive labels are used to assign net classes to individual nets. They can also be used to assign net classes and component classes to nets and symbols, respectively, inside rule areas. Only one label type is visible in the toolbar at a time; you can expand the palette to choose another tool by clicking and holding/dragging. |

|

Place a rule area. |

|

Place a hierarchical subsheet. You must specify the file name for this subsheet. |

|

Place a hierarchical sheet pin on a sheet corresponding to a hierarchical label that has been added in the target sheet. |

|

Sync hierarchical sheet pins and hierarchical labels. This displays a list of all the hierarchical labels in each subsheet and lets you manage the corresponding hierarchical sheet pins. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note: Lines are graphical objects and are not the same as wires placed with the Wire tool. They do not connect anything. |

|

|

|

Delete clicked items. |

Grids and snapping

Schematic elements such as symbols, wires, text, and graphic lines are snapped to the grid when moving, dragging, and drawing them. Additionally, the wire and label tools snap to other connected items such as pins, wires, and labels even when grid snapping is disabled.

Both grid and connected object snapping can be disabled while moving the mouse by using the modifier keys in the table below.

| On Apple keyboards, use the Cmd key instead of Ctrl. |

| Modifier Key | Effect |

|---|---|

Ctrl |

Disable grid snapping. |

Shift |

Disable connected object snapping. |

The default grid size is 50 mil (0.050") or 1.27 millimeters. This is the recommended grid for placing symbols and wires in a schematic and for placing pins when designing a symbol in the Symbol Editor. Smaller grids can also be used, but this is intended only for text and symbol graphics, and not recommended for placing pins and wires.

| Wires connect with other wires or pins only if their ends coincide exactly. Therefore it is very important to keep symbol pins and wires aligned to the grid. It is recommended to always use a 50 mil grid when placing symbols and drawing wires because the KiCad standard symbol library and all libraries that follow its style also use a 50 mil grid. Using a grid size other than 50 mil will result in schematics without proper connectivity! |

| Symbols, wires, and other elements that are not aligned to the grid can be snapped back to the grid by selecting them, right clicking, and clicking Align Elements to Grid. |

You can adjust the grid size by right-clicking and selecting a new grid from the list in the Grid submenu. Pressing the n or N hotkeys will cycle to the next and previous grid in the list, respectively.

You can also select a new grid or edit the available grids in the Grids pane

of the preferences dialog. As a shortcut to reach this dialog, right click the

![]() button on the left toolbar and

select Edit Grids….

button on the left toolbar and

select Edit Grids….

In this dialog you can select an active grid from the list of grids, reorder the

list of grids (![]() /

/ ![]() ),

and add (

),

and add (![]() ), remove (

), remove (![]() ),

or edit (

),

or edit (![]() ) grids. Grids defined in this

dialog can have unequal X and Y spacing as well as an optional name. The grid

spacing and name are specified when you create or edit a grid.

) grids. Grids defined in this

dialog can have unequal X and Y spacing as well as an optional name. The grid

spacing and name are specified when you create or edit a grid.

This dialog also lets you designate two grids from the list as "Fast Grids", which can be quickly selected using Alt+1 and Alt+2.

Finally, you can configure grid overrides for different types of objects. Grid

overrides let you set particular grid sizes for different types of objects which

will be used instead of the default grid when working with those objects. For

example, you can set a 50 mil grid for wires and connected items while using

smaller grids to finely position text and graphics. Grid overrides can be

individually enabled and disabled in this dialog, or globally enabled and

disabled using the

![]() button on

the left toolbar (Ctrl+Shift+G).

button on

the left toolbar (Ctrl+Shift+G).

The visual appearance of the grid can also be customized in several ways. You can change the thickness of the grid markings, switch their shape (dots, lines, or crosses), and set the minimum displayed spacing in the Display Options page of the preferences dialog, and you can change the grid color in the Colors page of the preferences dialog.

The grid can be shown or hidden using the

![]() button on the left-hand

toolbar. By default the grid is still active even if it is hidden, but this is

configurable in the Display Options preferences page. There you can set the

grid to be disabled when it is hidden or even disable the grid entirely.

button on the left-hand

toolbar. By default the grid is still active even if it is hidden, but this is

configurable in the Display Options preferences page. There you can set the

grid to be disabled when it is hidden or even disable the grid entirely.

Editing object properties

All objects have properties that are editable in a dialog. Use the hotkey E or select Properties from the right-click context menu to edit the properties of selected item(s). You can only open the properties dialog if all the items you have selected are of the same type. For many object types, like symbols, you can only edit the properties of a single item at one time. To edit the properties of multiple items at once, including items with different types, you can use the Properties Manager.

You can only use the properties dialog to edit one item at a time. To edit multiple items, use the Properties Manager, described below. There are also other tools that can be used to edit specific types of objects in bulk, such as the Edit Text and Graphics tool for editing visual properties of text, symbol fields, labels, and graphic shapes, or the Symbol Fields Table for editing symbol fields in bulk.

You can also view and edit item properties using the Properties Manager. The Properties Manager is a docked panel that displays the properties of the selected item or items for editing. If multiple types of items are selected at once, the properties panel displays only the properties shared by all of the selected item types.

Editing a property in the Properties Manager immediately applies the change. When multiple items are selected, property modifications are applied to each selected item individually, not to the whole selection as a group. For example, when changing the orientation of multiple items, each item is individually rotated around its own origin, not the group’s origin.

Show the Properties Manager with View → Panels → Properties or the

![]() button on the left toolbar.

button on the left toolbar.

In properties dialogs and many other dialogs, any field that contains a numeric value can also accept a basic math expression that results in a numeric value.

For example, a dimension may be entered as 2 * 2mm, resulting in a value of

4mm. Basic arithmetic operators as well as parentheses for defining order of

operations are supported. Units can also be specified, and unit conversions are

performed automatically, so 1in + 1mm evaluates to 26.4mm.

Working with symbols

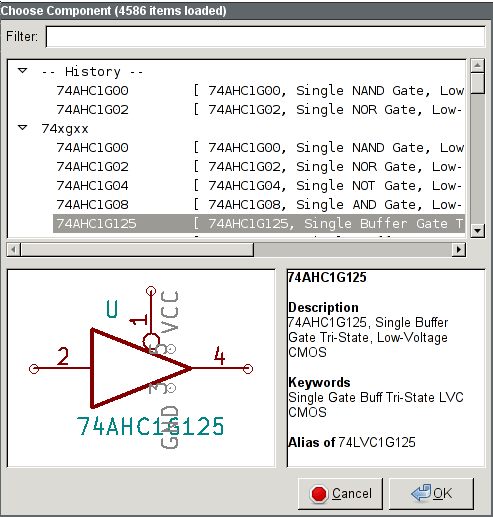

Placing symbols

To place a symbol in your schematic, use the

![]() button or the A

hotkey. The Choose Symbols dialog appears and lets you select a symbol to add.

Symbols are grouped by symbol library.

button or the A

hotkey. The Choose Symbols dialog appears and lets you select a symbol to add.

Symbols are grouped by symbol library.

By default, only the symbol/library name and description columns are shown. Additional columns can be added by right-clicking the column header and selecting Select Columns.

The Choose Symbol dialog filters symbols by name, keywords, description, and

all additional symbol fields according to what you type into the search field.

You can choose to sort search results alphabetically or by best match by

clicking on the ![]() button.

button.

Some advanced filters are available:

-

Wildcards:

*matches any number of any characters, including none, and?matches any single character. -

Key-value pairs: if a library part’s description or keywords contain a tag of the format "Key:123", you can match relative to that by typing "Key>123" (greater than), "Key<123" (less than), etc. Numbers may include one of the following case-insensitive suffixes:

p

n

u

m

k

meg

g

t

10-12

10-9

10-6

10-3

103

106

109

1012

ki

mi

gi

ti

210

220

230

240

-

Regular expressions: if you’re familiar with regular expressions, these can be used too. The regular expression flavor used is the wxWidgets Advanced Regular Expression style, which is similar to Perl regular expressions.

If the symbol specifies a default footprint, this footprint will be previewed in the lower right. If the symbol includes footprint filters, alternate footprints that satisfy the footprint filters can be selected in the footprint dropdown menu at right.

After selecting a symbol to place, the symbol will be attached to the cursor. Left clicking the desired location in the schematic places the symbol into the schematic. Before placing the symbol in the schematic, you can rotate it, mirror it, and edit its fields, by either using the hotkeys or the right-click context menu. These actions can also be performed after placement.

If the Place repeated copies option is checked, after placing a symbol KiCad will start placing another copy of the symbol. This process continues until the user presses Esc.

For symbols with multiple units, if the Place all units option is checked, after placing the symbol KiCad will start placing the next unit in the symbol. This continues until the last unit has been placed or the user presses Esc.

Placing power symbols

A power symbol is a symbol representing a connection to a

power net. The symbols are grouped in the power library, so they can be

placed using the symbol chooser. However, as power placements are frequent, the

![]() tool is available. This tool

is similar, except that the search is done directly in the

tool is available. This tool

is similar, except that the search is done directly in the power library and

any other library that contains power symbols.

Moving symbols

Symbols can be moved using the Move (M) or Drag (G) tools. These tools act on the selected symbol, or if no symbol is selected they act on the symbol under the cursor.

The Move tool moves the symbol itself without maintaining wired connections to the symbol pins.

The Drag tool moves the symbol without breaking wired connections to its pins, and therefore moves the connected wires as well.

You can also Drag symbols by clicking and dragging them with the mouse, depending on the Left button drag gesture setting in the Mouse and Touchpad section of Preferences.

Symbols can also be rotated (R) or mirrored in the X (X) or Y (Y) directions.

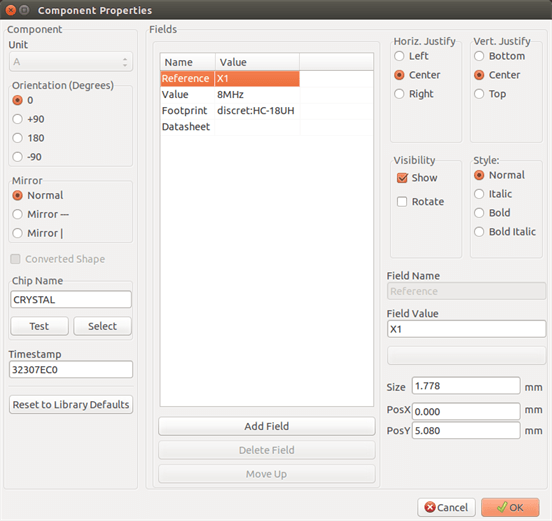

Editing symbol properties

Symbols in the schematic can be individually edited, both in terms of their properties (fields, attributes, etc.) and in terms of their pins and graphics. Editing a symbol in the schematic only affects that particular instance of the symbol; it does not affect any other copies of that symbol in the schematic, and it does not affect the library symbol.

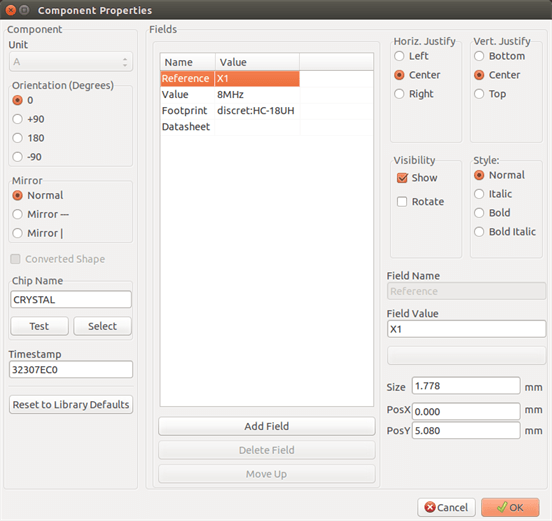

To edit the properties of a symbol in the schematic, open its properties dialog (E). You can also double-click the symbol.

The majority of the settings in this dialog are the same as in the symbol editor. You can edit the symbol’s fields, attributes, pin functions, and embedded files, as in the symbol editor.

The Symbol Properties window displays all the fields of a symbol in a table. New

fields can be added, and existing fields can be deleted, edited, reordered,

moved, or resized. Fields can be arbitrarily named, but names beginning with

ki_, e.g. ki_description, are reserved by KiCad and should not be used for

user fields. All symbol fields will be added to the symbol’s corresponding

footprint when the PCB is updated from the schematic.

Each field’s name and value can be visible or hidden, and there are several formatting options: horizontal and vertical alignment, orientation, position, font, text color, text size, and bold/italic emphasis. Field autoplacement can also be enabled on a per-field basis. The displayed position is always indicated for a normally displayed symbol (no rotation or mirroring) and is relative to the anchor point of the symbol.

| Formatting options for symbol fields can be shown or hidden by right-clicking on the header row of the symbol field table and enabling or disabling the desired columns. Not all columns are shown by default. |

Several fields have special behavior:

-

The Footprint field defines which footprint will correspond to the symbol in the board design. When the footprint field is selected, you can click the

button to open the

footprint chooser to assign a

footprint to the symbol. See the Assigning Footprints

section for other ways to assign footprints.

button to open the

footprint chooser to assign a

footprint to the symbol. See the Assigning Footprints

section for other ways to assign footprints. -

The Datasheet field can contain the manufacturer’s datasheet for the symbol. You can right click a symbol in the editing canvas and choose Show Datasheet (D) to open the datasheet listed in the symbol. A symbol’s datasheet can be a local file or a file at a remote URL, like the manufacturer’s website. You can choose a local file using a file browser by selecting the datasheet field in the symbol’s properties, then clicking the

button. If you enable the Embed File

checkbox in the file browser, the datasheet will be embedded in the schematic

instead of being referenced as an an external file. This means the datasheet

will be available on any computer. For more information, see the

embedded files documentation.

button. If you enable the Embed File

checkbox in the file browser, the datasheet will be embedded in the schematic

instead of being referenced as an an external file. This means the datasheet

will be available on any computer. For more information, see the

embedded files documentation.

Symbols have several attributes that affect how the symbols are treated by other parts of KiCad.

-

Exclude from simulation prevents the symbol from being included in SPICE simulations. Symbols that are excluded from simulation are drawn with a grey outline around them and a simulation waveform icon to their bottom right, as shown below. The color of the outline and icon is configurable by editing the "Excluded-from-simulation Markers" color in the selected colorscheme. The visual marker (the outline and the icon) can be disabled completely by disabling View → Mark items which are excluded from simulation.

-

Exclude from bill of materials prevents the component from being included in BOM exports.

-

Exclude from board means that the symbol is schematic-only, and a corresponding footprint will not be added to the PCB.

-

Do not populate means that the component should not be attached to the PCB, although a corresponding footprint should still be added to the board. DNP symbols appear desaturated and with a red "X" over them in the schematic, as shown below. The color of the "X" is configurable by editing the "DNP Markers" color in the selected colorscheme.

To edit the symbols’s form, i.e. its pins and graphics, you need to use the symbol editor. There are two buttons for opening a symbol in the editor, depending on whether you want to edit a single copy of a symbol in the schematic or a symbol’s source copy in the library.

-

Edit Symbol… will open the specific instance of the symbol in the symbol editor. Editing this symbol will only affect this one instance of the symbol in the schematic. It will not affect other instances of the symbol in the schematic, and it will not affect the library copy of the symbol. You can also open a schematic symbol in the symbol editor by right clicking the symbol in the schematic and selecting Edit with symbol editor (Ctrl+E).

-

Edit Library Symbol… will open the library copy of the symbol in the symbol editor. Editing the library copy of the symbol will edit the symbol in the symbol library, but will not immediately affect any instances of that symbol in the schematic. To update symbols in the schematic with changes to the library symbol, use the Update Symbol from Library… tool. Editing the library symbol in this way is equivalent to opening the symbol editor, opening the appropriate symbol in its library, and editing it.

The Update Symbol from Library… button is used to update the schematic’s copy of the symbol to match the copy in the library. The Change Symbol… button is used to swap the current symbol to a different symbol in the library. These functions are described later.

The Simulation Model… button opens the Simulation Model Editor for specifying the symbol’s behavior in SPICE simulations.

Editing symbol fields individually

An individual symbol text field can be edited directly with the E hotkey (with a field selected instead of a symbol) or by double-clicking on the field.

Some symbol fields have their own hotkey to edit them directly. With the symbol selected, the Reference, Value, and Footprint fields can be edited with the U, V, or F hotkeys, respectively.

The options in this dialog are the same as those in the full Symbol Properties dialog, but are specific to a single field.

Symbol fields can be automatically moved to an appropriate location with the Autoplace Fields action (select a symbol and press O). Field autoplacement is configurable in the Schematic Editor’s Editing Options, including a setting to always autoplace fields. You can also disable autoplacement for individual fields in the Symbol Properties or Field Properties dialogs.

Alternate pin functions

Symbol pins can have alternate pin functions defined for them. Alternate pin functions allow you to select a different name, electrical type, and graphical style for a pin when a symbol has been placed in the schematic. This can be used for pins that have multiple functions, such as microcontroller pins.

Alternate pin functions are selected once a symbol has been placed in the schematic. The pin function is selected in the Pin Functions tab of the Symbol Properties dialog. Alternate definitions are selectable in the dropdown in the Alternate Assignment column. You can also select an alternate pin by right-clicking the pin and selecting a new function from the Pin Function menu.

Pins that have alternate functions available are displayed with a small graphical indicator next to the pin name, as shown in the screenshot below. To globally show or hide these indicators, use View → Show Pin Alternate Icons.

For information on how to add alternate pin functions to symbols, see the symbol editor documentation.

Updating and exchanging symbols

When a symbol is added to the schematic, KiCad embeds a copy of the library symbol in the schematic so that the schematic is independent of the system libraries. Symbols that have been added to the schematic are not automatically updated when the library changes. Library symbol changes are manually synced to the schematic so that the schematic does not change unexpectedly.

| You can use the Compare Symbol with Library tool to inspect the differences between a symbol in a schematic with its corresponding library symbol. |

To update symbols in the schematic to match the corresponding library symbol, use Tools → Update Symbols from Library…, or right click a symbol and select Update Symbol…. You can also access the tool from the symbol properties dialog.

The top of the dialog has options to choose which symbols will be updated:

-

Update all symbols in schematic: all symbols in the schematic will be updated to match the library versions of the symbols.

-

Update selected symbol(s): symbols that are selected in the schematic will be updated.

-

Update symbols matching reference designator: symbols matching the specified reference designator will be updated. The reference designator field supports wildcards:

*matches any number of any characters, including none, and?matches any single character. -

Update symbols matching value: symbols with the specified value will be updated. The value field supports wildcards:

*matches any number of any characters, including none, and?matches any single character. -

Update symbols matching library identifier: symbols that match the specified library identifier will be updated. Library identifiers consist of the symbol library name and the symbol name, separated by

:.

The middle of the dialog has options to control what parts of the symbol will be updated. On the left, you can select which fields will be modified (updated or reset). On the right, you can select how to update those fields:

-

Remove fields if not in library symbol: if selected, any fields that are in the schematic version of the symbol but not the library version will be deleted.

-

Reset fields if empty in library symbol: if selected, any fields that are empty in the library version of the symbol will be set to empty in the schematic version of the symbol.

-

Update/reset field text: if selected, field contents in the schematic version of the symbol will be updated to match the fields in the library version of the symbol. Any fields that are empty in the library version of the symbol will not be updated unless Reset fields if empty in library symbol is selected.

-

Update/reset field visibilities: if selected, fields in the schematic version of the symbol will have their visibility updated to match the library version of the symbol.

-

Update/reset field text sizes and styles: if selected, fields in the schematic version of the symbol will have their text sizes and styles updated to match the library version of the symbol.

-

Update/reset field positions: if selected, fields in the schematic version of the symbol will be moved to match the locations of the fields in the library version of the symbol.

-

Update symbol shape and pins: the symbol’s shape and pins are always updated to match the library version of the symbol.

-

Update keywords and footprint filters: The symbol’s keywords and footprint filters are always updated to match the library version of the symbol.

-

Update/reset pin name/number visibilities: if selected, the visibility of pin names and numbers in the schematic version of the symbol will be updated to match the visibility of the pin names and numbers in the library version of the symbol.

-

Reset alternate pin functions: if selected, alternate pin functions selected for the symbol’s pins will be reset to default pin functions.

-

Update/reset symbol attributes: if selected, the schematic symbol attributes (do not populate, exclude from simulation, exclude from BOM, exclude from board) will be updated to match the library version of the symbol.

-

Reset custom power symbols: if selected, the

Valuefield of power symbols in the schematic will be updated to match the library versions of the symbols. If not selected, theValuefield of power symbols will not be updated, even if theValuefield of other non-power symbols would be updated. Note that changing theValuefield of power symbols will change the global net associated with the power symbol.

The bottom of the dialog displays messages describing the update actions that have been performed, with filters for which types of messages to display (errors, warnings, actions, and/or infos).

To change an existing symbol to a different symbol, use Edit → Change Symbols…, or right click an existing symbol and select Change Symbol…. This dialog is also accessible from the symbol properties dialog.

The options for the Change Symbols dialog are very similar to the Update Symbols from Library dialog.

Another way to swap existing symbols for new ones is to use Tools → Edit Symbol Library Links…. This dialog contains a table of every symbol in the design, grouped by current library symbol. By choosing a new symbol in the New Library Reference column, you can make all instances of the existing symbol instead point to the new symbol. If the Update symbol fields from new library option is used, the contents of the existing symbols' fields will be updated to match the new symbols' fields.

The Map Orphans button attempts to automatically remap orphaned symbols to

symbols with the same name in an active library. For example, if there is a symbol

with the current library reference mylib:symbol123, but the mylib library

cannot be found, the Map Orphans button will attempt to find a symbol named

symbol123 in any of the libraries that are present. This button is only

enabled if orphaned symbols are present in the schematic (see the

legacy schematics section).

This dialog is primarily useful for managing symbols that appear in multiple libraries, when you want to switch from one library to another. For example, if a schematic uses symbols that are in both a global library and a project-specific library, the Symbol Library References dialog could be used to switch between using the global symbols or the equivalent project-specific symbols. It does not have features for fine-grained control of how fields are updated; for that, use the Change Symbols dialog.

Comparing symbols between schematic and library

When a symbol in a schematic diverges from the corresponding symbol in the original symbol library, you can use the Compare Symbol with Library tool to inspect the differences between the two versions of the symbol. Run the tool using Inspect → Compare Symbol With Library.

The Summary tab shows the name of the symbol, including its library and schematic reference designator, and provides a list of the differences between the schematic and library versions of the symbol.

The Visual tab shows a visual comparison of the schematic and library versions of the symbol. This can be used as a visual diff tool.

By default, the comparison displays both versions of the symbol superimposed on each other. To see the changes more easily, you can drag the slider at the bottom of the tab to the right to emphasize the library version of the symbol in the superimposed view (making the schematic version of the symbol more transparent) or drag it to the left to emphasize the schematic version (making the library version more transparent). At the far right and left ends of the slider, the schematic and library versions of the symbol, respectively, are fully hidden. It may be helpful to drag the slider back and forth to see the changes more clearly.

You can press the A/B button, or use the / hotkey, to quickly toggle back and forth between the schematic and library versions.

The Update Symbol from Library… button opens the Update Symbol from Library tool to update the symbol to match the library.

The screenshot above shows a visual comparison with the schematic version of the symbol deemphasized. You can see a partially transparent pin 5 (from the schematic version of the symbol) is in a different location than the fully opaque pin 5 (from the library symbol). This indicates that the pin was moved in either the schematic or library version of the symbol.

Symbol Fields Table

The Symbol Fields Table allows you to view and modify field values for all

symbols in a spreadsheet interface.

The Symbol Fields Table also acts as a BOM export tool.

You can open the Symbol Fields Table with the

![]() button.

button.

The main table has a row for each symbol and a column for each field. Each cell is editable.

Cells are navigated with the arrow keys, or with Tab / Shift+Tab to move right / left and Enter to move down, respectively.

A range of cells can be selected by clicking and dragging. The whole range of selected cells will be copied (Ctrl+C) or pasted into (Ctrl+V) on a copy or paste action. Copying a range of cells from the table can be useful for creating a BOM. More details of copying and pasting cells are described below.

The left pane contains a list of all available symbol fields, as well as some

virtual fields such as Quantity and Item

Number. You can add or remove any symbol field from the main table on using the

Include checkboxes (fields can also be shown or hidden by right-clicking on the

header of the main table). New symbol fields can be added using the

![]() button; a field with that name

will be added to every symbol. To rename the field, which changes the field name

in all symbols, use the

button; a field with that name

will be added to every symbol. To rename the field, which changes the field name

in all symbols, use the ![]() button. The

button. The ![]() button deletes

the field from all symbols.

You can collapse this panel by clicking the

button deletes

the field from all symbols.

You can collapse this panel by clicking the ![]() button.

button.

Each field has its own column label, which is displayed at the top of the corresponding column in the symbol fields table and in exported BOMs. The column label for each field is shown in the second column of in the left pane. A column label does not have to match the field name. To change a field’s column label, click in the BOM Name column for that field, then enter a new name.

Similar symbols can optionally be grouped by any symbol field using the Group

By checkboxes. Symbols are grouped into a single row in the table if all of

their Group By fields are identical. The grouped row can be expanded to show

the individual symbols by clicking the arrow at the left of the row.

The Group symbols checkbox enables or disables symbol grouping,

and the ![]() button recalculates groupings.

button recalculates groupings.

Presets are available to configure the list of fields. Presets store which fields are displayed, which fields are used for grouping, and the column order. You can create and save your own presets or use one of several default presets. Custom presets can be deleted in this dialog or in the Schematic Setup dialog.

Symbols can be filtered by reference designator using the Filter textbox at

the top. The filter supports wildcards: * matches any number of any

characters, including none, and ? matches any single character.

You can also change the display scope using the dropdown menu to the right of the filter box. You can show only symbols in the current sheet, the current sheet and all of its subsheets, or the entire project.

The ![]() menu contains some additional options for showing or hiding symbols.

menu contains some additional options for showing or hiding symbols.

-

Include 'DNP' Symbols includes or excludes symbols with the Do Not Populate attribute from both the Edit tab and any BOM exports.

-

Include 'Exclude from BOM' Symbols includes or excludes symbols with the Exclude from BOM attribute from the Edit tab. Symbols with the Exclude from BOM attribute are always excluded from BOM exports.

You can cross-probe from this dialog by selecting a row in the table.

Depending on the cross-probe options selected in the ![]() menu,

this can highlight the corresponding symbol in the schematic,

select the corresponding symbol in the schematic, or do nothing.

The selection action can also select the symbol’s footprint in the board editor,

depending on the PCB Editor cross-probing settings configured in Preferences.

menu,

this can highlight the corresponding symbol in the schematic,

select the corresponding symbol in the schematic, or do nothing.

The selection action can also select the symbol’s footprint in the board editor,

depending on the PCB Editor cross-probing settings configured in Preferences.

The Symbol Fields Table is also a bill of materials tool. You can use the Export button to save the symbol fields to an external file. The fields are exported to the BOM exactly as they are currently shown in the spreadsheet view. File format settings are configured in the Export tab. For more information about exporting a BOM, see the BOM tool documentation.

Virtual fields

If you create a field in the Symbol Fields Table whose name begins with a

text variable, a virtual field will be created. Virtual

fields have a value that is evaluated for each symbol based on the contents of

the field name. For example, a virtual field named ${SYMBOL_NAME} will

evaluate to the symbol’s name for each symbol. A virtual field can contain any

text, as long as it starts with a text variable, so a virtual field named

${SYMBOL_LIBRARY}:${SYMBOL_NAME} will evaluate to <library name>:<symbol

name> for each symbol.

Virtual fields exist only in the Symbol Fields Table and in BOM exports. While they are displayed as a column in the dialog and BOMs, and they can be used to group or sort symbols in BOM exports just like regular fields, adding a virtual field in the Symbol Fields Table does not add a corresponding field to each symbol in the schematic.

Any text variable can be used in virtual fields, including sheet and project text variables.

Text variables that correspond to symbol attributes (${DNP},

${EXCLUDE_FROM_BOARD}, ${EXCLUDE_FROM_SIM}, ${EXCLUDE_FROM_BOM}) are

displayed specially. In the Symbol Fields Table, they are shown as checkboxes

for each symbol that directly set or unset the corresponding symbol attribute.

In BOM exports, they expand to the friendly name of the attribute if the attribute is

set (e.g. Excluded from board for

${EXCLUDE_FROM_BOARD} and DNP for ${DNP}) or to an empty string if the attribute is not set.

Finally, there are two special virtual fields that can be created:

-

${QUANTITY}is a virtual field that contains the number of grouped instances of each symbol. -

${ITEM_NUMBER}is a virtual field that contains the row number of each symbol in the table.

Tricks to simplify filling fields

There are several special copy/paste methods in the spreadsheet for pasting values into larger regions, including auto-incrementing pasted cells. These features may be useful when pasting values that are shared in several symbols.

These methods are illustrated below.

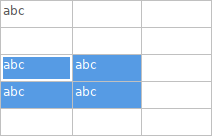

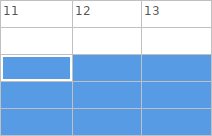

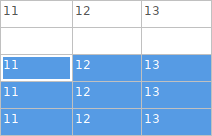

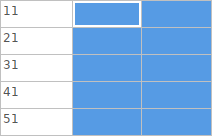

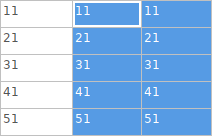

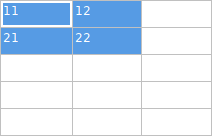

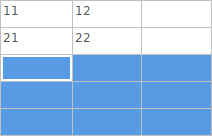

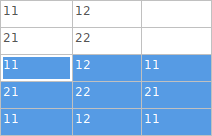

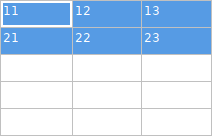

| 1. Copy (Ctrl+C) | 2. Select target cells | 3. Paste (Ctrl+V) |

|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| These techniques are also available in other dialogs with a grid control element. |

Reference designators and symbol annotation

Reference designators are unique identifiers for components in a design. They are often printed on a PCB and in assembly diagrams, and allow you to match symbols in a schematic to the corresponding components on a board.

In KiCad, reference designators consist of a letter indicating the type of

component (R for resistor, C for capacitor, U for IC, etc.) followed by a

number. If the symbol has multiple units then the reference designator will also

have a trailing letter indicating the unit. Symbols that don’t have a reference

designator set have a ? character instead of the number. Reference designators

must be unique.

Reference designators can be automatically set when symbols are added to the schematic, and you can set or reset reference designators yourself by manually editing an individual symbol’s reference designator field or in bulk using the Annotation tool.

| The process of setting a symbol’s reference designator is called annotation. |

Auto-annotation

When auto-annotation is enabled, symbols will be automatically annotated when

they are added to the schematic. You can enable auto-annotation by checking the

Automatically annotate symbols checkbox in the Schematic Editor →

Editing Options pane in Preferences. Auto-annotation can also be

toggled using the ![]() button

in the left toolbar.

button

in the left toolbar.

There are options to control how symbols are automatically annotated in the Annotation page of Schematic Setup.

-

When multiple symbols are added simultaneously, they are annotated according to the Order setting, sorted by either X or Y position.

-

The Numbering option sets the starting number for new reference designators. This can be the lowest available number, or a number based on the sheet number. When Allow reference reuse is enabled, reference designators can be automatically assigned as long as they are not currently used by another symbol. When disabled, a reference designator can never be used again once it has been assigned to a symbol, even if it is not currently in use.

For more information about annotation options, see the documentation for the Annotation page of Schematic Setup.

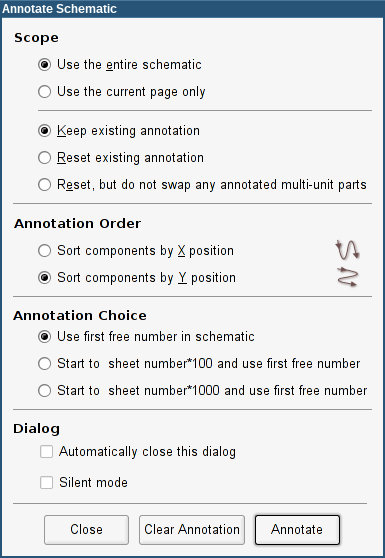

Annotation tool

The Annotation tool assigns reference designators to symbols in the schematic.

To launch the Annotation tool, click the ![]() button in the top toolbar.

button in the top toolbar.

The tool provides several options to control how symbols are annotated.

Scope: Selects whether annotation is applied to the entire schematic, to only the current sheet, or to only the selected symbols. If the Recurse into subsheets option is selected, symbols in subsheets of the selected scope will be reannotated; otherwise symbols in subsheets will not be reannotated. For example, if Recurse into subsheets and Selection only selected, symbols in any selected subsheets will be reannotated.

Options: Selects whether annotation should apply to all symbols and reset existing reference designators, or apply only to unannotated symbols. If the Reset symbol units option is enabled, symbol units will be reannotated individually. This means symbol units may be grouped into symbols differently after reannotation. When it is disabled, each symbol’s units will be reannotated as a group so that they remain together as units of the same symbol.

Order: Chooses the direction of numbering. If symbols are sorted by X position, all symbols on the left side of a schematic sheet will be lower numbered than symbols on the right side of the sheet. If symbols are sorted by Y position, all symbols on the top of a sheet will be lower numbered than symbols at the bottom of the sheet.

Numbering: Selects the starting point for numbering reference designators. The lowest unused number above the starting point is picked for each reference designator. The starting point can be an arbitrary number (typically zero), or it can be the sheet number multiplied by 100 or 1000 so that each part’s reference designator corresponds to the schematic page it is on.

The Clear Annotation button clears all reference designators in the selected scope.

Annotation messages can be filtered with the checkboxes at the bottom or saved to a report using the Save… button.

Electrical connections

Electrical connections in KiCad are known as nets, where each net represents a circuit node. All symbol pins on the same net are considered electrically connected.

There are two primary ways to establish connections: wires and labels. Wires make direct connections between symbol pins and other wires, while labels connect to other labels with the same name. Both wires and labels are shown in the schematic below.

Connections can also be made with buses and with implicit connections via hidden power pins.

Net name assignment rules

Every net in the schematic is assigned a name, whether that name is specified by the user (using a label) or automatically generated by KiCad.

When multiple labels are attached to the same net, the final net name is determined in the following order, from highest priority to lowest:

-

-

Output sheet pins are higher priority than Input sheet pins

-

If there are multiple labels of one type attached to a net, the names are sorted alphabetically and the first is used.

If a net travels through multiple sheets of a hierarchy, it will take its name from the highest level of the hierarchy where it has a hierarchical label or local label. As usual, local labels take priority over hierarchical labels.

If none of the label types above are attached to a net, the net’s name is automatically generated based on the connected symbol pins.

Wires

Wires are used to directly establish electrical connections between two points. To establish a connection, a segment of wire must be connected by its end to another segment or to a pin. Only wire ends create connections; if a wire crosses the middle of another wire, a connection will not be made.

Unconnected wire ends have a small square that indicates the connection point. The square disappears when a connection is made to the wire end. Unconnected pins have a circle, which also disappears when a connection is made.

| Wires connect with other wires or pins only if their ends coincide exactly. Therefore it is important to keep symbol pins and wires aligned to the grid. It is recommended to always use a 50 mil grid when placing symbols and drawing wires because the KiCad standard symbol library and all libraries that follow its style also use a 50 mil grid. |

| Symbols, wires, and other elements that are not aligned to the grid can be snapped back to the grid by selecting them, right clicking, and selecting Align Elements to Grid. |

Drawing and editing wires

To begin connecting elements with wire, use the Wire tool

![]() in the right toolbar

(w). Wires can also be automatically started by clicking on an unconnected

symbol pin or wire end.

in the right toolbar

(w). Wires can also be automatically started by clicking on an unconnected

symbol pin or wire end.

You can restrict wires to 90 degree angles using the

![]() button in the left

toolbar, or to 45 degree angles with the

button in the left

toolbar, or to 45 degree angles with the

![]() button. The

button. The

![]() button allows you to

place wires at any angle. You can cycle through these modes using

Shift+Space, or select the desired mode in Preferences → Schematic

Editor → Editing Options. These modes affect

graphic lines in addition to wires.

button allows you to

place wires at any angle. You can cycle through these modes using

Shift+Space, or select the desired mode in Preferences → Schematic

Editor → Editing Options. These modes affect

graphic lines in addition to wires.

As in the PCB editor, the / hotkey switches wire posture.

Wires can be moved and edited using the Move (M) or Drag (G) tools. As with symbols, the Move tool moves only the selected segment, without maintaining existing connections to other segments. The Drag tool maintains existing connections.

You can select connected wires using the Select Connection tool (Alt+4). This tool selects all connected wire segments until it reaches a junction, starting with the selected segment or the segment under the cursor. Using the tool again expands the existing selection to the next junction.

You can break a wire segment into two pieces by right-clicking a wire and selecting Slice. The segment will be separated at the current mouse position. You can also separate a wire segment from the adjacent segments by right-clicking the segment and selecting Break.

Normally the line style of a wire follows the

net’s net class settings (nets are in the

Default net class if no other net class is specified). However, the line style

for the selected wire segments can be overridden in the wire’s properties dialog

(E when a wire segment is selected). The wire’s width, color, and line

style (solid, dashed, dotted, etc.) can be set. Setting the width to 0,

clearing the color, and using the Default line style uses the default width,

color, and style, respectively, from the net class settings. If a wire junction

is included in the selection, the junction size can also be edited here.

Wire junctions

Wires that cross are not implicitly connected. It is necessary to

join them by explicitly adding a junction dot if a connection is desired

(![]() button in the right

toolbar). Junction dots will be automatically added to wires that start or end

on top of an existing wire.

button in the right

toolbar). Junction dots will be automatically added to wires that start or end

on top of an existing wire.

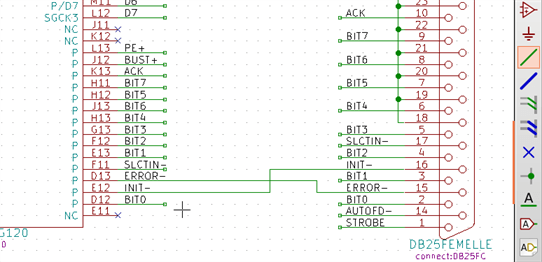

Junction dots are used in the schematic figure above on the wires connected to

P1 pins 18, 19, 20, 21, 22, and 23.

Junction size automatically follows the schematic’s Junction dot size

setting in Schematic Setup → General → Formatting. Color follows

the net class setting. The automatic

size and color can be overridden in each junction dot’s properties; a size of

0 is equivalent to the schematic default size, and clearing the color uses the

net class color.

Wire hop-overs

When wires cross without a junction dot, they do not connect. By default, this is drawn simply as one wire crossing through the other wire. However, you can configure such crossovers to be visually indicated with hop-overs instead of simple intersections, as shown in the schematic below. The size of hop-overs is configurable for a given schematic; all hop-overs in the schematic have the same size.

To enable display of hop-overs, open the Formatting page of Schematic Setup and change the Hop-over size setting from None to another size.

Labels

Labels are used to assign net names to wires and pins. Wires with the same net name are considered to be connected, so labels can be used to make connections without drawing direct wire connections.

A net can only have one name. If two different labels are placed on the same net, an ERC violation will be generated. Only one of the net names will be used in the netlist. The final net name is determined according to the rules described below.

There are three types of labels, each with a different connection scope.

-

Local labels, also referred to simply as labels, only make connections within a sheet. Add a local label with the

button in the right

toolbar.

button in the right

toolbar. -

Global labels make connections anywhere in a schematic, regardless of sheet. Add a global label with the

button in the right

toolbar.

button in the right

toolbar. -

Hierarchical labels connect to hierarchical sheet pins and are used in hierarchical schematics for connecting child sheets to their parent sheet. Add a hierarchical label with the

button in the right toolbar.

button in the right toolbar.

| Labels that have the same name will connect, regardless of the label type, if they are in the same sheet. |

| You can convert from one type of label to another type of label using the Change To tools. |

Adding and editing labels

After using the appropriate button or hotkey to create a label, the Label Properties dialog appears.

The Label field sets the label’s name, which determines the net that the label assigns to its attached wire or pin. You can choose a label name from a list of nets that are already in the schematic by clicking the dropdown menu next to the label name field.

| Net names can contain any character, including spaces and other special characters. |

Label text supports markup for overbars, subscripts, etc., as well as variable substitution. Use the Syntax help link in the dialog for a summary.

When the Multiple label input option is enabled, the Label field supports entering multiple labels, with one label on each line. In this case, the dialog will create multiple independent labels in sequence, one per line.

| Multiple label input may be useful for copying labels from other sources, such as a spreadsheet. |

There are several options to control the label’s appearance. You can change the font, size, and color of the text, and set bold and italic emphasis. You can also set the orientation of the text relative to the label’s connection point. Hierarchical and global labels have several additional options: the Auto option automatically sets the label orientation based on the connected schematic elements, and Shape option controls the shape of the label outline (Input, Output, Bidirectional, Tri-state, or Passive). The outline shape is purely visual and has no electrical consequence.

| The default text size can be set for a schematic in Schematic Setup, and the default font can be set in Preferences. |

| Global labels have additional settings to control margins around the label text in the Schematic Setup dialog. |

Labels can also have fields added to them. Two fields have special meaning (Net

Class and Sheet References, described below), but arbitrary fields can also

be added. Label fields behave like symbol fields:

you can show or hide their name and value and adjust the alignment, orientation,

position, size, font, color, and emphasis.

| Formatting options for label fields can be shown or hidden by right-clicking on the header row of the label field table and enabling or disabling the desired columns. Not all columns are shown by default. |

Like symbol fields, label fields can be edited individually by opening the properties of a specific label field from the schematic (double click the label field, or use E).

After accepting the label properties, the label is attached to the cursor for placement. The connection point for a label is the small square in the corner of the label. The square disappears when the label is connected to a wire or the end of a pin. If multiple labels were specified in the dialog, each label is attached to the cursor for placement after the previous label is placed.

The connection point’s position relative to the label text can be changed by choosing a different label orientation in the label’s properties, or by mirroring/rotating the label.

The Label Properties dialog can be accessed at any time by selecting a label and using the E hotkey, double-clicking on the label, or with Properties… in the right-click context menu.

Assigning net classes with labels

In addition to assigning net names, labels can be used to assign net classes. A

label field named Net Class assigns the specified net class to the net

associated with the label. To make it easier to assign net classes in this way,

Net Class is the default name for new label fields, and Net Class fields

present a dropdown list of all the net classes that have been specified in

Schematic Setup or

Board Setup.

You can also type in a net class that isn’t explicitly listed in the Schematic/Board Setup priority list. Such implicit net classes can’t be assigned any design settings, like net class color or track width, but they can still be used in DRC rule queries.

If multiple Net Class fields are added to a label, or multiple

labels with Net Class fields are applied to a net, all of the specified net

classes are assigned to the net.

For more information about assigning net classes, see the net class documentation.

Inter-sheet references

Global labels can display inter-sheet references, which are a list of page numbers for other places in the schematic where the same global label appears. Clicking an inter-sheet reference travels to the listed page. If multiple references are listed, clicking the reference list brings up a menu to select the desired page.

Inter-sheet references are globally controlled in the Schematic Setup window’s Formatting page. References can be enabled or disabled, and the displayed format for the list can be adjusted, including with optional prefix or suffix characters.

The image below shows a global label with inter-sheet references to two other

schematic pages. A prefix and suffix of [ and ], respectively, were added in

Schematic Setup.

A Sheet References field with value ${INTERSHEET_REFS} is automatically

added to global labels, and is used to control the appearance of inter-sheet

references for that label. The ${INTERSHEET_REFS} text variable gets expanded

to the full list of inter-sheet references for the global label, as configured

in Schematic Setup. Visibility of inter-sheet references is globally controlled

in Schematic Setup rather than with the Sheet References field visibility

control. The Sheet References field has no meaning for other types of labels.

Buses

Buses are a way to group related signals in the schematic in order to

simplify complicated designs. Buses can be drawn like wires using the

bus tool ![]() , and are named using

labels the same way signal wires are.

, and are named using

labels the same way signal wires are.

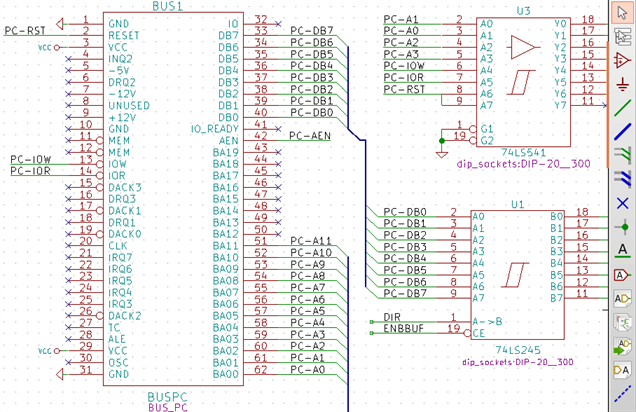

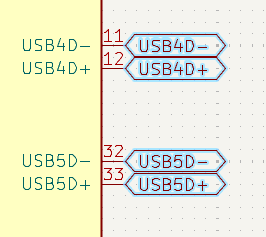

In the following schematic, many pins are connected to buses, which are the thick blue lines in the center.

Bus members

There are two types of bus in KiCad 6.0 and later: vector buses and group buses.

A vector bus is a collection of signals that start with a common prefix

and end with a number. Vector buses are named <PREFIX>[M..N] where

PREFIX is any valid signal name, M is the first suffix number, and N

is the last suffix number. For example, the bus DATA[0..7] contains the

signals DATA0, DATA1, and so on up to DATA7. It doesn’t matter which

order M and N are specified in, but both must be non-negative.

Vector bus prefixes cannot contain the characters {, }, [, or ], except as part of markup for superscripts, subscripts, overbars, or text variables.

Prefixes may contain spaces, but the spaces must be escaped.

You can escape spaces in the prefix either by preceding the space with a backslash (\) or by surrounding the entire prefix with double quotes (").

For example, DATA\ BUS[0..7] and "DATA BUS"[0..7] are both valid vector bus names.

A group bus is a collection of one or more signals and/or vector buses. Group buses can be used to bundle together related signals even when they have different names. Group buses use a special label syntax:

<OPTIONAL_NAME>{SIGNAL1 SIGNAL2 SIGNAL3}

The members of the group are listed inside curly braces ({}) separated

by space characters. An optional name for the group goes before the opening

curly brace. If the group bus is unnamed, the resulting nets on the PCB

will just be the signal names inside the group. If the group bus has a

name, the resulting nets will have the name as a prefix, with a period (.)

separating the prefix from the signal name.

For example, the bus {SCL SDA} has two signal members, and in the netlist

these signals will be SCL and SDA. The bus USB1{DP DM} will generate

nets called USB1.DP and USB1.DM. For designs with larger buses that are

repeated across several similar circuits, using this technique can save time.

Group buses can also contain vector buses. For example, the bus

MEMORY{A[7..0] D[7..0] OE WE} contains both vector buses and plain signals,

and will result in nets such as MEMORY.A7 and MEMORY.OE on the PCB.

Group bus names cannot contain the characters {, }, [, or ], except as part of markup for superscripts, subscripts, overbars, or text variables.

Group bus names and the constituent net names may contain spaces, but the spaces must be escaped.

You can escape spaces either by preceding the space with a backslash (\) or by surrounding the entire group bus name or net name with double quotes (").

For example, DATA\ BUS{SIGNAL\ 1 SIGNAL\ 2}, "DATA BUS"{"SIGNAL 1" "SIGNAL 2"}, and "DATA BUS"{SIGNAL\ 1 "SIGNAL 2"} are all valid (and equivalent) labels for group buses.

Bus wires can be drawn and connected in the same manner as signal wires, including using junctions to create connections between crossing wires. Like signals, buses cannot have more than one name — if two conflicting labels are attached to the same bus, an ERC violation will be generated.

Connections between bus members

Pins connected between the same members of a bus must be connected by labels. It is not possible to connect a pin directly to a bus; this type of connection will be ignored by KiCad.

In the example above, connections are made by the labels placed on wires connected to the pins. Bus entries (wire segments at 45 degrees) to buses are graphical only, and are not necessary to form logical connections.

In fact, using the repetition command (Insert), connections can be very quickly made in the following way, if component pins are aligned in increasing order (a common case in practice on components such as memories, microprocessors…):

-

Place the first label (for example

PCA0) -

Use the repetition command as much as needed to place members. KiCad will automatically create the next labels (

PCA1,PCA2…) vertically aligned, theoretically on the position of the other pins. -

Draw the wire under the first label. Then use the repetition command to place the other wires under the labels.

-

If needed, place the bus entries by the same way (Place the first entry, then use the repetition command).

|

In the Schematic Editor → Editing Options section of the Preferences menu, you can set the repetition parameters:

|

Bus unfolding

The unfold tool allows you to quickly break out signals from a bus. To unfold a signal, right-click on a bus object (a bus wire, etc) and choose Unfold from Bus. Alternatively, use the Unfold Bus hotkey (default: C) when the cursor is over a bus object. The menu allows you to select which bus member to unfold.

After selecting the bus member, the next click will place the bus member label at the desired location. The tool automatically generates a bus entry and wire leading up to the label location. After placing the label, you can continue placing additional wire segments (for example, to connect to a component pin) and complete the wire in any of the normal ways.

Bus aliases

Bus aliases are shortcuts that allow you to work with large group buses more efficiently. They allow you to define a group bus and give it a short name that can then be used instead of the full group name across the schematic.

To create bus aliases, open the Bus Alias Definitions pane in Schematic Setup.

An alias may be named any valid signal name. Using the dialog, you can add

signals or vector buses to the alias. As a shortcut, you can type or paste