|

| def | __init__ (self, *args) |

| |

| "bool" | LoadFromFile (self, *args) |

| |

| "BOARD_STACKUP const &" | GetStackupDescriptor (self, *args) |

| |

| "SEVERITY" | GetSeverity (self, "int" aDRCErrorCode) |

| |

| "bool" | Ignore (self, "int" aDRCErrorCode) |

| |

| "NETCLASSES &" | GetNetClasses (self) |

| |

| "void" | SetNetClasses (self, "NETCLASSES" aNetClasses) |

| |

| "ZONE_SETTINGS &" | GetDefaultZoneSettings (self) |

| |

| "void" | SetDefaultZoneSettings (self, "ZONE_SETTINGS" aSettings) |

| |

| "NETCLASS *" | GetDefault (self) |

| |

| "wxString const &" | GetCurrentNetClassName (self) |

| |

| "bool" | UseNetClassTrack (self) |

| |

| "bool" | UseNetClassVia (self) |

| |

| "bool" | UseNetClassDiffPair (self) |

| |

| "int" | GetBiggestClearanceValue (self) |

| |

| "int" | GetSmallestClearanceValue (self) |

| |

| "int" | GetCurrentMicroViaSize (self) |

| |

| "int" | GetCurrentMicroViaDrill (self) |

| |

| "unsigned int" | GetTrackWidthIndex (self) |

| |

| "void" | SetTrackWidthIndex (self, "unsigned int" aIndex) |

| |

| "int" | GetCurrentTrackWidth (self) |

| |

| "void" | SetCustomTrackWidth (self, "int" aWidth) |

| |

| "int" | GetCustomTrackWidth (self) |

| |

| "unsigned int" | GetViaSizeIndex (self) |

| |

| "void" | SetViaSizeIndex (self, "unsigned int" aIndex) |

| |

| "int" | GetCurrentViaSize (self) |

| |

| "void" | SetCustomViaSize (self, "int" aSize) |

| |

| "int" | GetCustomViaSize (self) |

| |

| "int" | GetCurrentViaDrill (self) |

| |

| "void" | SetCustomViaDrill (self, "int" aDrill) |

| |

| "int" | GetCustomViaDrill (self) |

| |

| "bool" | UseCustomTrackViaSize (self, *args) |

| |

| "unsigned int" | GetDiffPairIndex (self) |

| |

| "void" | SetDiffPairIndex (self, "unsigned int" aIndex) |

| |

| "void" | SetCustomDiffPairWidth (self, "int" aWidth) |

| |

| "int" | GetCustomDiffPairWidth (self) |

| |

| "void" | SetCustomDiffPairGap (self, "int" aGap) |

| |

| "int" | GetCustomDiffPairGap (self) |

| |

| "void" | SetCustomDiffPairViaGap (self, "int" aGap) |

| |

| "int" | GetCustomDiffPairViaGap (self) |

| |

| "bool" | UseCustomDiffPairDimensions (self, *args) |

| |

| "int" | GetCurrentDiffPairWidth (self) |

| |

| "int" | GetCurrentDiffPairGap (self) |

| |

| "int" | GetCurrentDiffPairViaGap (self) |

| |

| "void" | SetMinHoleSeparation (self, "int" aDistance) |

| |

| "void" | SetCopperEdgeClearance (self, "int" aDistance) |

| |

| "void" | SetSilkClearance (self, "int" aDistance) |

| |

| "LSET" | GetEnabledLayers (self) |

| |

| "void" | SetEnabledLayers (self, "LSET" aMask) |

| |

| "bool" | IsLayerEnabled (self, "PCB_LAYER_ID" aLayerId) |

| |

| "int" | GetCopperLayerCount (self) |

| |

| "void" | SetCopperLayerCount (self, "int" aNewLayerCount) |

| |

| "int" | GetBoardThickness (self) |

| |

| "void" | SetBoardThickness (self, "int" aThickness) |

| |

| "int" | GetDRCEpsilon (self) |

| |

| "int" | GetHolePlatingThickness (self) |

| |

| "int" | GetLineThickness (self, "PCB_LAYER_ID" aLayer) |

| |

| "wxSize" | GetTextSize (self, "PCB_LAYER_ID" aLayer) |

| |

| "int" | GetTextThickness (self, "PCB_LAYER_ID" aLayer) |

| |

| "bool" | GetTextItalic (self, "PCB_LAYER_ID" aLayer) |

| |

| "bool" | GetTextUpright (self, "PCB_LAYER_ID" aLayer) |

| |

| "int" | GetLayerClass (self, "PCB_LAYER_ID" aLayer) |

| |

| "void" | SetAuxOrigin (self, "wxPoint" aOrigin) |

| |

| "wxPoint const &" | GetAuxOrigin (self) |

| |

| "void" | SetGridOrigin (self, "wxPoint" aOrigin) |

| |

| "wxPoint const &" | GetGridOrigin (self) |

| |

| "void" | CloneFrom (self, "BOARD_DESIGN_SETTINGS" aOther) |

| |

|

| | thisown = property(lambda x: x.this.own(), lambda x, v: x.this.own(v), doc="The membership flag") |

| |

| | m_TrackWidthList = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TrackWidthList_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TrackWidthList_set, doc=) |

| |

| | m_ViasDimensionsList = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_ViasDimensionsList_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_ViasDimensionsList_set, doc=) |

| |

| | m_DiffPairDimensionsList = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DiffPairDimensionsList_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DiffPairDimensionsList_set, doc=) |

| |

| | m_MicroViasAllowed = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasAllowed_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasAllowed_set, doc=) |

| |

| | m_BlindBuriedViaAllowed = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_BlindBuriedViaAllowed_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_BlindBuriedViaAllowed_set, doc=) |

| |

| | m_CurrentViaType = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_CurrentViaType_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_CurrentViaType_set, doc=) |

| |

| | m_UseConnectedTrackWidth = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_UseConnectedTrackWidth_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_UseConnectedTrackWidth_set, doc=) |

| |

| | m_TempOverrideTrackWidth = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TempOverrideTrackWidth_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TempOverrideTrackWidth_set, doc=) |

| |

| | m_MinClearance = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MinClearance_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MinClearance_set, doc=) |

| |

| | m_TrackMinWidth = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TrackMinWidth_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TrackMinWidth_set, doc=) |

| |

| | m_ViasMinAnnularWidth = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_ViasMinAnnularWidth_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_ViasMinAnnularWidth_set, doc=) |

| |

| | m_ViasMinSize = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_ViasMinSize_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_ViasMinSize_set, doc=) |

| |

| | m_MinThroughDrill = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MinThroughDrill_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MinThroughDrill_set, doc=) |

| |

| | m_MicroViasMinSize = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasMinSize_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasMinSize_set, doc=) |

| |

| | m_MicroViasMinDrill = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasMinDrill_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MicroViasMinDrill_set, doc=) |

| |

| | m_CopperEdgeClearance = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_CopperEdgeClearance_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_CopperEdgeClearance_set, doc=) |

| |

| | m_HoleClearance = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_HoleClearance_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_HoleClearance_set, doc=) |

| |

| | m_HoleToHoleMin = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_HoleToHoleMin_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_HoleToHoleMin_set, doc=) |

| |

| | m_SilkClearance = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_SilkClearance_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_SilkClearance_set, doc=) |

| |

| | m_DRCSeverities = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DRCSeverities_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DRCSeverities_set, doc=) |

| |

| | m_DrcExclusions = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DrcExclusions_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DrcExclusions_set, doc=) |

| |

| | m_ZoneFillVersion = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_ZoneFillVersion_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_ZoneFillVersion_set, doc=) |

| |

| | m_ZoneKeepExternalFillets = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_ZoneKeepExternalFillets_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_ZoneKeepExternalFillets_set, doc=) |

| |

| | m_MaxError = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_MaxError_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_MaxError_set, doc=) |

| |

| | m_SolderMaskMargin = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_SolderMaskMargin_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_SolderMaskMargin_set, doc=) |

| |

| | m_SolderMaskMinWidth = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_SolderMaskMinWidth_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_SolderMaskMinWidth_set, doc=) |

| |

| | m_SolderPasteMargin = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_SolderPasteMargin_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_SolderPasteMargin_set, doc=) |

| |

| | m_SolderPasteMarginRatio = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_SolderPasteMarginRatio_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_SolderPasteMarginRatio_set, doc=) |

| |

| | m_DefaultFPTextItems = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DefaultFPTextItems_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DefaultFPTextItems_set, doc=) |

| |

| | m_LineThickness = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_LineThickness_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_LineThickness_set, doc=) |

| |

| | m_TextSize = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TextSize_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TextSize_set, doc=) |

| |

| | m_TextThickness = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TextThickness_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TextThickness_set, doc=) |

| |

| | m_TextItalic = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TextItalic_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TextItalic_set, doc=) |

| |

| | m_TextUpright = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_TextUpright_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_TextUpright_set, doc=) |

| |

| | m_DimensionUnitsMode = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionUnitsMode_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionUnitsMode_set, doc=) |

| |

| | m_DimensionPrecision = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionPrecision_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionPrecision_set, doc=) |

| |

| | m_DimensionUnitsFormat = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionUnitsFormat_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionUnitsFormat_set, doc=) |

| |

| | m_DimensionSuppressZeroes = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionSuppressZeroes_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionSuppressZeroes_set, doc=) |

| |

| | m_DimensionTextPosition = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionTextPosition_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionTextPosition_set, doc=) |

| |

| | m_DimensionKeepTextAligned = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionKeepTextAligned_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionKeepTextAligned_set, doc=) |

| |

| | m_DimensionArrowLength = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionArrowLength_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionArrowLength_set, doc=) |

| |

| | m_DimensionExtensionOffset = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionExtensionOffset_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_DimensionExtensionOffset_set, doc=) |

| |

| | m_HasStackup = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_HasStackup_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_HasStackup_set, doc=) |

| |

| | m_UseHeightForLengthCalcs = property(_pcbnew.BOARD_DESIGN_SETTINGS_m_UseHeightForLengthCalcs_get, _pcbnew.BOARD_DESIGN_SETTINGS_m_UseHeightForLengthCalcs_set, doc=) |

| |

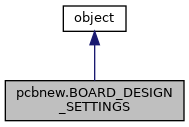

Proxy of C++ BOARD_DESIGN_SETTINGS class.

Definition at line 8893 of file pcbnew.py.